Indice:

Per capire cosa sono i processori e comprenderne le caratteristiche attuali, la cosa migliore è ripercorrere la storia della loro evoluzione attraverso quelle che sono state le tappe fondamentali.

Il primo microprocessore della storia nasce nel 1971, è prodotto dalla INTEL ed è il risultato di un progetto a cui partecipò l'italiano F.Faggin insieme a M.Hoff e S.Mazer. Poichè si tratta del progenitore di tutti i microprocessori forse merita un pò di spazio ed una piccola descrizione, che se interessa troverete alla pagina dedicata.Chi fosse ancora di più interessato all'evoluzione delle macchine da calcolo a partire dalle prime realizzazioni di tipo meccanico e, passando attraverso i primi elaboratori elettronici, arrivare ai giorni nostri può consultare il sito "Automazione delle macchine da calcolo".

I primi processori (più specificatamente microprocessori o CPU, Central Processing Unit) erano circuiti integrati al cui interno si potevano distinguere, in base alle loro funzioni essenziali, le seguenti parti:

alcuni registri per la memorizzazione temporanea dei dati da elaborare e dei risultati |

|

alcuni registri (puntatori) necessari alla gestione della memoria ed alla lettura/scrittura dei dati/istruzioni in essa |

|

una Unità di calcolo Logico-Aritmetico (ALU) in grado di compiere, come dice il nome, operazioni logiche (AND, OR, NOT, etc) e aritmetiche (somma, sottrazione, etc) |

|

una Unità di Controllo ( CU), vera "intelligenza" del sistema, in grado di "interpretare" (decodificare) il significato di una istruzione in codice macchina (binario) ed eseguire tutte le operazioni necessarie a portarla a termine. |

In una prima fase dell'evoluzione (dall'INTEL 4004 all'INTEL 8086/8088) l'architettura di un microprocessore è rimasta più o meno quella indicata e ciò che ha determinato un miglioramento degli stessi sono stati in sostanza:

la frequenza di funzionamento o frequenza di clock |

|

l'ampiezza del bus dati, che si rifletteva sulla grandezza dei dati direttamente manipolabili |

|

l'ampiezza del bus indirizzi, dal quale dipende la grandezza della memoria gestibile dal microprocessore |

Il computer fa il suo ingresso nella realtà quotidiana con la costruzione dei primi Home Computer, fra i quali ricordiamo quelli costruiti intorno allo ZILOG Z80 (SINCLAIR SPECTRUM, MSX TEXAS) od al Motorola 6510 (COMMODORE 64).

|

|

|

| Una "fetta" (wafer) di Silicio sulla quale sono realizzati molti microprocessori (ogni quadratino è un microprocessore) | Come si presentava il chip (uno dei "quadratini" della figura precedente) su cui era costruito lo Z80 |

Sia lo Z80 che il Motorola 6510 erano processori ad 8 bit (bus dati) con bus indirizzi a 16 bit; le frequenze di funzionamento si attestavano intorno ai 2-4 Mhz. La grandezza massima di un numero direttamente manipolabile era dunque 28-1 = 255 (ma ovviamente con metodi software si potevano utilizzare numeri di qualsiasi grandezza); l'ampiezza massima della memoria gestibile era invece 216 = 65.536 byte = 64 KB. La struttura di questi Home Computer era molto semplice: il microprocessore, un po' di memoria ROM per contenere lo scarno sistema operativo (se così si poteva chiamare), la memoria RAM ed interfacce per i dispositivi di Ingresso/uscita, che si potevano elencare in tastiera, lettore a cassette e televisore.CPU, memorie ed interfacce comunicavano fra loro tramite i due bus nominati, più alcuni segnali di controllo; esattamente il bus dati serviva per il trasferimento dei dati dall'uno all'altro dispositivo ed il bus indirizzi per individuare la sorgente (da dove prendere il dato) o la destinazione del dato, con la collaborazione dei segnali di controllo.

L'INTEL 8086, progenitore di tutti i processori INTEL successivi 80286, 80386, 80486 ed anche in qualche modo dei Pentium, era, invece, un microprocessore con frequenza massima di funzionamento di 10 Mhz, bus dati a 16 bit e bus indirizzi 20 bit. La grandezza massima di un numero direttamente manipolabile era dunque 216-1 = 65.535, l'ampiezza massima della memoria gestibile era invece 220 = 1.048.576 = 1 MB.

Frequenza di funzionamento, ampiezza del bus dati (o lunghezza di parola) e ampiezza del bus indirizzi rimangono parametri importanti per la valutazione della qualità di un microprocessore, ma la loro evoluzione ha fatto marcare altre notevoli caratteristiche. I rapidi miglioramenti delle prestazioni dei microprocessori sono dovuti essenzialmente a tre fattori:

Il progresso nella tecnologia di fabbricazione dei chip, passata in pochi anni da 0,8 micron per i primi Pentium ai 0,25 micron degli AMD K6-3D e dei primi Pentium III, dove la distanza in mm misura l'occupazione lineare di un transistor integrato; più piccolo è questo valore più alto è il numero di transistor integrati per mm2 di Silicio. La maggiore integrazione dei transistor consente un innalzamento della frequenza di lavoro dell'integrato. |

|

Modifiche dell'architettura dei microprocessori che li hanno portati ad essere sempre più efficiente nell'esecuzione dei programmi. |

|

Nel passaggio da un mP di una generazione al successivo il set di istruzioni dei microprocessori è stato continuamente ampliato |

Vale la pena soffermarsi sul secondo punto, prendendo come esempio dell'evoluzione, la storia dei microprocessori INTEL, senz'altro quelli più affermati nel campo dei PC.

Fino allo ZILOG Z80 ogni mP eseguiva un'istruzione sostanzialmente in due fasi: FETCH ed EXECUTE. Nella fase di fetch il mP reperiva l'istruzione da eseguire in memoria e ne trasferiva il codice operativo al suo interno in un registro detto Registro Istruzione. Nella seconda fase decodificava il codice operativo, eseguiva l'istruzione e memorizzava il risultato. Le due fasi erano eseguite sequenzialmente e solo al termine il mP procedeva all'istruzione successiva.

Nell'INTEL 8086/88 si ha una sostanziale prima modifica dell'architettura del microprocessore con la divisione della CPU in 2 unità funzionali, una preposta alla operazione di fetch (BIU, Bus Interface Unit) e l'altra a quella di esecuzione (EU, Execute Unit). Le due unità potendo operare separatamente, permettevano di anticipare la fase di fetch dell'istruzione successiva durante l'esecuzione dell'istruzione precedente; questo meccanismo produceva una maggiore velocità del microprocessore nell'esecuzione del programma.

Inoltre per consentire all'EU di avere a disposizione sempre tutti i byte necessari all'espletamento di un'istruzione, era prevista una piccola memoria interna (6 byte per l'8086, 4 per l'8088), detta coda per il suo modo di funzionare (First In First Out), che era riempita e rinnovata continuamente dalla BIU con i byte di programma da eseguire prelevati dalla memoria. In questo modo la EU aveva sempre disponibile all'interno della CPU stessa una piccola parte del programma da eseguire (salvo il caso in cui l'istruzione in corso non prevedesse un salto).

Il meccanismo della coda è stato mantenuto sostanzialmente inalterato nei microprocessori successivi, salvo il crescere del numero di byte della stessa.

Viceversa la sequenza che porta al completamento di un'istruzione è stata nei microprocessori successivi parcellizzata e distinta in più fasi (oltre a quella di fetch ed execute già viste), ciascuna delle quali è compiuta da un'unità opportuna. Questo ha velocizzato ulteriormente il lavoro della CPU (Per fare un esempio semplice dei vantaggi della suddivisione dei compiti supponiamo di dover prendere da una tavola e lavare dei piatti sporchi. Le operazioni da compiere possono essere distinte in: 1 - prendere il piatto e portarlo sul lavello, 2 - lavare il piatto, 3 - sciacquarlo, 4 - asciugarlo e riporlo. Se si è da soli a fare il lavoro dovremo, rispettando la sequenza, giungere all'asciugatura e messa a posto del primo piatto prima di procedere con il successivo, ma se siamo in 4 amici, ognuno può incaricarsi di una delle 4 fasi, allora quando il primo piatto giunge all'asciugatura, il secondo sarà in fase di risciacquo, il terzo starà per essere lavato ed il quarto starà per essere portato sul lavello. Il lavoro sarà sicuramente più veloce.) Questa organizzazione del lavoro della CPU viene indicata con il termine di pipeline e viene sviluppato ulteriormente a partire dall'80386.Un esempio di fasi esecutive di una pipeline può essere:

Fetch istruzione

Decodifica istruzione

Fetch operando

Esecuzione istruzione

Memorizzazione risultato

Con il crescere della frequenza di funzionamento della CPU sono cresciuti i problemi di colloquio fra questa e le memorie. Infatti per non avere rallentamenti nelle operazioni di lettura/scrittura in memoria occorre che il tempo di accesso di una memoria sia dell'ordine di qualche periodo di clock. Le memorie dinamiche, con le quali sono realizzate le RAM in quanto più economiche, ad un certo punto dell'evoluzione sono diventate lente rispetto alle velocità del mP. Il problema è stato risolto con il ricorso a memorie statiche, più veloci ma anche più costose; pertanto, scartato per ragioni economiche l'ipotesi di costituire tutta la memoria RAM con memorie statiche, si è affiancata alla RAM dinamica una porzione di memoria statica, denominata memoria cache. Il funzionamento della memoria cache è il seguente: nel momento in cui esegue la prima istruzione di un programma il mP trasferisce dalla RAM dinamica alla cache tutta la parte di programma successiva all'istruzione (fino a riempire la cache); in questo modo, nel presupposto logico che le istruzioni da eseguire successivamente saranno quelle già trasferite nella cache, il mP andrà a cercare dapprima in questa, con tempi di accesso nettamente inferiori, l'istruzione da eseguire successivamente; il risultato di questo ricerca è il più delle volte positivo e solo nel caso in cui l'istruzione in corso sia un salto (passaggio) ad una parte di programma fuori della cache, la CPU dovrà ricorrere alla lettura della RAM dinamica e contemporaneamente aggiornare la cache col meccanismo già illustrato.

La cache vede la sua comparsa con i sistemi 386 e sarà quella che viene ora denominata cache di 1° livello. Successivamente nei mP 486 la cache di 1° livello verrà integrata nella CPU (8 KB per dati e programma), mentre esternamente la CPU verrà affiancata con una cache di 2° livello. Con la versione CELERON A (MENDOCINO) anche la cache di 2° livello verrà integrata nella CPU.

In presenza delle due cache il processore opera inizialmente cercando i dati nella cache di 1° livello; nel caso in cui i dati non siano presenti il mP prende in esame la cache esterna e qualora i dati siano presenti in questa, il controllore della cache li trasferisce ed aggiorna la cache di 1° livello. Nel caso in cui i dati non siano reperibili in nessuna delle cache (circa il 2% dei casi) il controllore ricava i dati dalla memoria di sistema e contemporaneamente li fornisce al mP aggiornando entrambe le cache.

A partire dall'INTEL 80286 (ma più efficacemente con l'80386) i mP sono in grado di funzionare in multitasking, cioè gestire più processi/compiti (lavori, più semplicemente) contemporaneamente, come ad esempio stampare un documento mentre si continua ad adoperare il Word processor. Per funzionare in questo modo, il microprocessore deve assegnare ad ogni processo una parte di memoria, non modificabile dagli altri processi (protected mode); inoltre, poiché la contemporanea esecuzione di molti compiti può richiedere molta memoria, qualora la memoria richiesta complessivamente ecceda quella disponibile, deve essere in grado di operare lo swapping , ovvero di trasferire su disco fisso parte del contenuto della memoria, occupata da un processo, in modo da liberarla per quello a cui serve, salvo recuperare quel contenuto al momento opportuno. Va infatti precisato che l'esecuzione contemporanea di più compiti è tale solo agli occhi dell'utente, in quanto in realtà il mP lavora, con la tecnica del time sharing, ad un processo alla volta, saltando da un processo all'altro e dedicando a ciascuno una piccola porzione di tempo secondo un ordine di priorità (come un cameriere che deve servire più tavoli, divide il suo tempo fra i diversi tavoli, prestando più attenzione alle richieste più urgenti).

Fino all'80386 (anzi fino all versione SX del 80486) ogni microprocessore della serie X86 poteva essere affiancato da un coprocessore matematico, (un altro microprocessore) il cui compito era di eseguire le operazioni matematiche, nella fattispecie quelle in virgola mobile (FPU, Floating Point Unit) ovvero con numeri non interi, ovviamente velocizzandone l'esecuzione. Dalla CPU 80486DX il coprocessore viene integrato nello stesso chip del mP. Il 486 come architettura è in sostanza un 386 a cui è stato affiancato il coprocessore matematico.

Le prime frequenze di clock del 486 sono 25, 33 e 50 Mhz, ma successivamente verranno presentate le versioni 486DX2 e 486DX4, che hanno per la prima volta la particolarità di avere un clock interno differente dal clock della scheda madre. La tecnologia costruttiva delle schede madri non permetteva a quei tempi, 1989, di portare il clock di sistema oltre i 33-50 Mhz, per cui le CPU venivano fatte funzionare con un clock che si otteneva per moltiplicazione di quello di sistema. Come la sigla implicitamente indica un 486DX4 viaggiava ad una frequenza (ideale) 4 volte superiore a quella di sistema e quindi a 100 Mhzcon clock di sistema a 25 Mhz, mentre un 486DX2 lavorava alla frequenza di 66 Mhz con clock di sistema a 33 Mhz.

Il 1992 vede la nascita del Pentium, il quale è in sostanza un doppio 486 ovvero contiene al suo interno due canali di processo (pipeline) sostanzialmente identici a quelli del 486 in grado di processare contemporaneamente 2 istruzioni alla volta (quando il programma lo consente). Le prime versioni del Pentium lavorano a 66, 100 Mhz.

Passando attraverso le versioni MMX e Pro, si arriva nella prima metà del 1997 al Pentium II che assomma molte novità importanti, mutuate dalle due versioni precedenti:

Il processore è in grado di eseguire il set di istruzioni MMX introdotte con il Pentium MMX e appositamente implementate per programmi che fanno uso intensivo di grafica e mezzi multimediali. La sigla può essere decifrata in Multi Media eXtension, ma, con riferimento alla singola istruzione più importante, anche in Matrix Multiplying eXtension, che sottolinea come queste istruzioni siano orientate al calcolo matriciale, usato intensivamente in tutte le applicazioni di grafica tridimensionale.In particolare nel Pentium II vengono introdotte istruzioni di tipo SIMD, Single Instruction Multiple Data, che consentono di eseguire la stessa operazione su blocchi multipli di dati. |

|

L'architettura, detta di tipo superscalare , prevede 6 pipeline di processo distinte e in grado di lavorare in parallelo, ognuna con funzioni specifiche (STORE DATA, STORE ADDRESS, LOAD ADDRESS, ALU integer,FPU, MMX unit) |

|

La macchina è in realtà un processore RISC (Reduced Instruction Set Computing) in grado di eseguire un codice X86 (codice di microprocessore CISC, Complex Instrution Set Computing) dopo un processo hardware di conversione del codice |

|

La cache di 1° livello è portata a 32 KB distinti in 16 KB per i dati e 16 KB per il programma |

|

Ci sono 8 registri a 64 per l'elaborazione MMX. |

|

La frequenza di clock prevista già inizialmente è così alta (mentre le frequenze delle mother board rimangono sui 50-66 Mhz) da indurre la INTEL a inserire il Pentium II in un nuovo contenitore (SECC, Single Edge Contacts Cartridge, che si inserisce in un connettore denominato SLOT1) su una piccola scheda che alloggia anche la cache di 2° livello (512 KB); CPU e cache sono collegate da un bus locale che lavora alla metà della frequenza del microprocessore, distinto dal bus che collega la CPU al sistema (mother board); questo tipo di soluzione viene denominata Dual Indipendent Bus (DIB). |

|

Il bus dati è a 64 bit, mentre il bus indirizzi è a 32 bit |

|

Il mP è costruito in tecnologia 0,28 micron. |

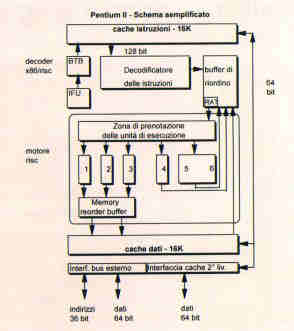

In figura è riportato uno schema semplificato dell'architettura del Pentium II.

|

I blocchi numerati da 1 a 6 hanno le seguenti funzioni:

Mentre le funzioni degli altri blocchi non definiti sono: BTB: Branch Target Buffer IFU: Instruction Fetch Unit RAT: Register Alias Table

|

Un particolare, evidenziato anche nello schema, che va sottolineato, perché verrà corretto dal successivo Pentium III è che la FPU e la MMX unit utilizzano lo stesso insieme di registri; questo ovviamente non consente alle due unità di lavorare sempre contemporaneamente.

A fianco del Pentium II la INTEL, negli anni successivi, ha introdotto versioni più economiche del processore, i CELERON. I CELERON hanno la stessa architettura dei Pentium, ma sono inizialmente inseriti in una cartuccia priva di cache di 2° livello, appunto per avere un costo di produzione minore. Tuttavia queste prime versioni, per la mancanza di cache 2L, si rivelarono subito poco soddisfacenti e la INTEL successivamente ha prodotto una versione A, anche detta in codice MENDOCINO, che aveva la particolarità di essere il primo microprocessore in assoluto con cache di 2° livello integrata nel chip del mP (128 KB) e quindi funzionante alla stessa frequenza del mP.

Questa particolarità lo ha reso un buon processore dal punto di vista del rapporto costo/prestazioni in quanto maggiormente efficiente, a parità di clock, per tutte quelle applicazioni che non fanno ricorso intensivo ad un ampio trasferimento di dati dalla memoria; occorre tenere presente infatti che i Celeron utilizzano bus di sistema a 66 Mhz. Comunque l'efficienza di questo processore ha fatto supporre ad alcuni che la Intel non spingesse troppo sulle frequenze di lavoro per non spiazzare i più redditivi, dal punto di vista economico, Pentium II.

Il Celeron A è costruito con tecnologia 0,25 micron.

Links:

Pentium II: overview

Pentium II: istruzioni MMX

La scelta di INTEL di passare allo Slot1 con utilizzo della SEC, oltre che da ragioni tecniche (la cache di 2° livello collegata al mP con bus locale alla metà della frequenza del processore) è dettata anche da ragioni commerciali. Lo Slot1 è un brevetto con il quale INTEL cerca di mettere in difficoltà le case produttrici di microprocessori che gli hanno fatto concorrenza finora mettendo sul mercato processori simili ai suoi a costi più competitivi. Fra le case produttrici di questi microprocessori alternativi spicca la AMD che risponde alla INTEL mettendo sul mercato (dopo altri processori) il K6-II 3D Now, un mP che utilizza ancora l'inserimento tradizionale sulla scheda madre,ma che può lavorare con bus di sistema a 100 Mhz (socket Super 7). Le caratteristiche del K6-II 3D Now sono:

una cache di 1° livello di 64 KB integrata nel chip |

|

una architettura superscalare con unità di esecuzione che possono lavorare contemporaneamente. |

|

|

un set di istruzioni arricchito con 21 istruzioni 3D Now, per velocizzare le animazioni grafiche. Le istruzioni 3D Now costituiscono un'evoluzione delle istruzioni MMX di INTEL in quanto utilizzano numeri in virgola mobile a singola precisione invece di quelli interi. La loro struttura è di tipo SIMD. |

|

|

anche il K6 come il Pentium II è una macchina RISC che esegue codice X86 dopo decodifica hardware |

|

|

è costruito con tecnologia 0,25 micron |

|

|

le frequenze iniziali sono 266-300 Mhz |

Il K6 è un mP dal costo più basso del Pentium e dalle prestazioni molto simili, per cui ha ottenuto un buon successo per computer di fascia medio-bassa. Rispetto al Pentium II il K6 ha lo svantaggio di avere la cache di 2° livello sulla mother board e quindi di essere collegato ad essa alla frequenza di sistema.Comunque INTEL per controbattere la AMD ha introdotto i CELERON, dalle prestazioni più limitate rispetto al Pentium II, ma anche dal costo più contenuto e con la peculiarità di avere una cache di 2° livello integrata nel chip del microprocessore .

Links:

AMD K6-II 3D Now: overview

AMD K6-II 3D Now:istruzioni 3D Now

Qui possiamo far finire la storia dei microprocessori; siamo ormai nel 1998 e tutto ciò che segue non è più storia ma attualità.

Come si vede a questo punto ogni microprocessore ha molti aspetti peculiari e la scelta diventa complicata. Occorre infatti valutare in primo luogo:

la frequenza di funzionamento |

|

l'ampiezza della cache di 1° livello |

|

la situazione della cache di 2° livello (integrata/non integrata, di quale ampiezza) |

|

il set di istruzioni implementato, soprattutto con riferimento a quelle concepite per le applicazioni grafiche e multimediali ( MMX e 3D Now) tenendo presente che perchè il vantaggio da esse offerte sia reale occorre che i programmi sviluppati dalle software house ne facciano uso, cosa che non è mai vera al momento della loro introduzione. |

Il tutto va tuttavia considerato nell'ottica dell'uso che si fa del proprio computer. Se non adoperate programmi spinti di animazione grafica e se non siete sempre alla ricerca dell'ultimo strabiliante videogioco (tenendo presente che l'animazione grafica dipende comunque fortemente dalla scheda grafica), ma viceversa adoperate il computer per lavori di videoscrittura, calcolo, animazioni non spinte ed elaborazioni grafiche non sofisticate, ormai anche una CPU economica fa il caso vostro, poichè le sue prestazioni sono in ogni caso notevoli. Se invece volete il meglio, guardatevi in tasca e regolatevi di conseguenza.

In ogni caso per essere guidati nella scelta, al di là di tutte le caratteristiche dei mP, è bene che vi guardiate i risultati delle prove fatte da quasi tutte le riviste del settore, mediante appositi benchmark che forzano il PC ad eseguire intensivamente alcuni applicativi (nonchè games).