Generalità.

Il convertitore analogico-digitale, indicato come convertitore A/D o ADC (Analog Digital Converter), trasforma un segnale analogico in un segnale digitale.

Il convertitore digitale-analogico, indicato come convertitore D/A o DAC (Digital Analog Converter), esegue l’operazione inversa rispetto all’ADC. Questo trasforma il segnale digitale, fornitogli all'ingresso, in un segnale analogico.

Questi dispositivi hanno svariati utilizzi nel campo dell'elettronica; e molte volte vengono utilizzati entrambi in una stessa applicazione.

Il convertitore ADC A/D trasforma un segnale analogico in un codice binario. Il passaggio da un segnale analogico (cioè che assume svariati valori all’interno di un intervallo), ad una successione di codici binari avviene tramite un’operazione chiamata quantizzazione.

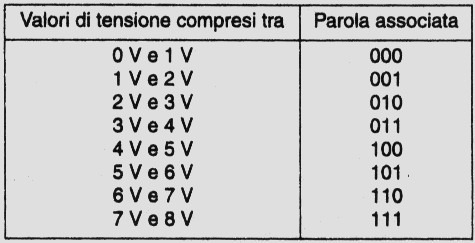

La quantizzazione è descritta dalla caratteristica di trasferimento rappresentata qui sotto :

I valori di tensione in ingresso sono riportati sull’ascissa, mentre sull’ordinata viene riportato il codice binario associato ad ogni intervallo di valori di Vi.

Nell’esempio in figura l’ampiezza massima del segnale d’ingresso è ViM = 8 V. Il numero di bit scelto è 3, quindi avremo una variazione binaria data dalla seguente formula : Q =ViM / 2 numero variabili = 8/23 = 8/8 = 1V (quindi avremo una variazione binaria ogni Volt).

A tutti i valori di tensione appartenenti ad un singolo intervallo degli otto possibili viene associato lo stesso codice o parola :

L’esempio mette in evidenza la necessità d’introdurre due parametri caratteristici dei convertitori A/D.

Il primo è l’ampiezza massima ViM del segnale d’ingresso che può essere convertito dall’ADC.

L’altro parametro è il numero n di bit con cui si effettua la codifica.

Caratteristiche degli ADC :

La risoluzione, indicata con R, rappresenta la variazione della tensione d’ingresso associata ad una variazione del bit meno significativo del codice binario.

La risoluzione è correlata al passo di quantizzazione.

R = Vim / 2n a 1 LSB

La risoluzione può essere espressa in percentuale :

R%= 100 x (Vim / 2n)

L’errore di quantizzazione, definisce il livello di indeterminazione ed è dovuto al fatto che ad ogni codice binario non viene associato un unico valore della tensione d’ingresso ma l’insieme dei valori appartenenti al passo di quantizzazione.

Quando il valore di Vi rappresentato dalla parola di codifica è l’estremo inferiore dell’intervallo, si ha l’errore massimo di quantizzazione (eM) e quindi:

eM = R

Il tempo di conversione è il tempo necessario all’ADC per trasformare il valore della tensione d’ingresso in un codice binario.

Il segnale analogico da convertire deve essere campionato per prelevare i valori della Vi da trasformare in codice binario. Con il campionamento il segnale analogico viene trasformato in una successione discreta di valori di bit.

La conversione deve terminare prima che arrivi il nuovo campione di tensione da convertire in codice binario.

Per lavorare con frequenze elevate è necessario inserire un dispositivo detto di sample/hold (campionamento e mantenimento). Altrimenti se il tempo di conversione è alto , c’è il rischio di perdere il nuovo campione perché la conversione precedente non è terminata. Per evitare ciò il valore viene memorizzato (hold) fino a quando deve essere convertito.

Secondo il teorema di Shannon la frequenza di campionamento fc deve essere maggiore di due volte la frequenza massima del segnale d'ingresso fMAX . Se abbiamo a che fare con un segnale non periodico, si deve considerare per fMAX la frequenza dell'armonica con frequenza più elevata.

Per avere una corretta frequenza di campionamento fc bisogna tener conto della seguente formula che fa emergere il tempo di acquisizione tac ; il tempo di ritardo per la memorizzazione (hold) ta e il tempo di conversione tc del nostro ADC,

quindi si avrà secondo Shannon : fc = 1 / 2 x ( tac + ta + tc )

Tipi di ADC :

Gli ADC flash sono convertitori veloci, infatti hanno tempi di conversione nell’ordine delle decine di nanosecondi, in modo da funzionare molto bene anche con segnali a frequenze elevate.

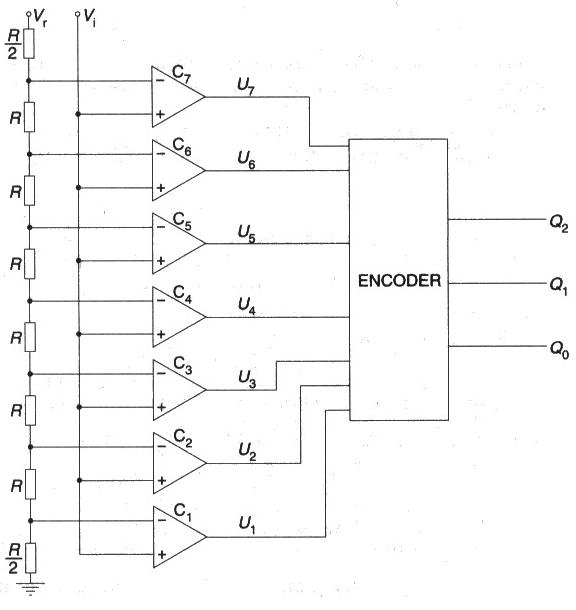

In figura è mostrato lo schema circuitale di principio di un ADC flash a 3 bit :

Il circuito è composto da 8 resistenze, 7 comparatori e un encoder con 7 ingressi e 3 uscite. Nel caso generale di ADC a n bit la struttura fondamentale è composta da 2n – 1 comparatori, 2n – 2 resistenze uguali di valore R, 2 resistenze di valore R/2 e 1 encoder. (n = numero di bit)

Questi convertitori presentano notevoli problemi costruttivi, essendo difficile ottenerli proprio con 2n – 2 resistenze uguali con stessa tolleranza; ne consegue che il dispositivo ha scarsa precisione oltre a risultare costoso.

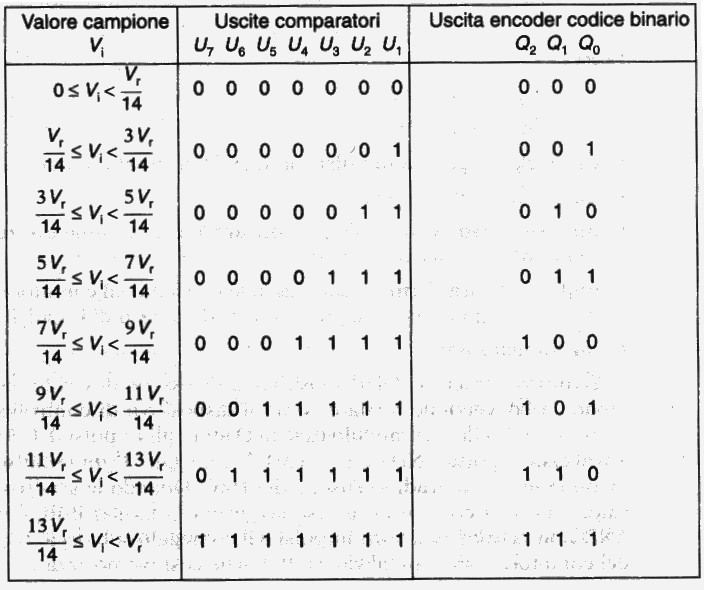

Il principio di funzionamento è basato sul confronto tra il valore del campione da convertire e i potenziali presenti sui morsetti invertenti dei comparatori dati dalla partizione di una tensione di riferimento Vr. In ogni comparatore, sul morsetto non invertente, è presente il valore di tensione da convertire: l’uscita è alta per il comparatore in cui si verifica che Vi è maggiore del potenziale del morsetto invertente.

Le uscite dei comparatori vanno in un encoder che fornisce così il codice binario.

Ad esempio, se i comparatori C1, C2, C3 hanno l’uscita alta, e tutti gli altri bassa, le uscite U1, U2, U3, U4, U5, U6, U7 valgono 1110000. L’encoder fornisce il seguente codice binario 011 (equivalente a 3 in decimale, pari al numero di comparatori con uscita alta).

Possiamo così costruire la seguente tabella (o matrice) di conversione :

Gli ADC two step sono convertitori che lavorano (come quello indicato qui sotto) nel campo di risoluzione del primo stadio di comparazione. In questo modo si risparmia un numero considerevole di comparatori rispetto all'ADC Flash. Per quest'ADC two step a 4 bit occorrono 3 + 3 comparatori (3 per il primo stadio e 3 per il secondo che lavora con Vs'), se avessimo usato un tradizionale ADC Flash avremmo avuto bisogno di 15 comparatori contro 6 di questo :

Il segnale analogico da convertire Va entra nel primo stadio di comparazione e allo stesso tempo in un A.O. (amplificatore operazionale) configurato in modo differenziale, che darà in uscita un segnale Vs'. Vs' farà lavorare il secondo stadio di comparazione. Ecco un esempio che ci farà capire il lavoro del primo e del secondo stadio di comparazione :

Tenendo conto che nel punto rosso si farà la conversione, si nota che il segnale Vs viene trattato dal primo stadio di comparazione (e avremo dalla conversione 11), mentre Vs' dal secondo (e avremo dalla conversione 01).

Da qui si nota che il primo stadio di comparazione determina i bit più significativi AB, mentre il secondo quelli meno significativi CD. Guardando i colori di questa tabella si può benissimo vedere come il secondo comparatore lavora nello stadio del primo :

|

Comparatore 1

|

Comparatore2

|

|||||

| A | B | C | D | |||

| 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 1 | |||

| 0 | 0 | 1 | 0 | |||

| 0 | 0 | 1 | 1 | |||

| 0 | 1 | 0 | 0 | |||

| 0 | 1 | 0 | 1 | |||

| 0 | 1 | 1 | 0 | |||

| 0 | 1 | 1 | 1 | |||

| 1 | 0 | 0 | 0 | |||

| 1 | 0 | 0 | 1 | |||

| 1 | 0 | 1 | 0 | |||

| 1 | 0 | 1 | 1 | |||

| 1 | 1 | 0 | 0 | |||

| 1 | 1 | 0 | 1 | |||

| 1 | 1 | 1 | 0 | |||

| 1 | 1 | 1 | 1 | |||

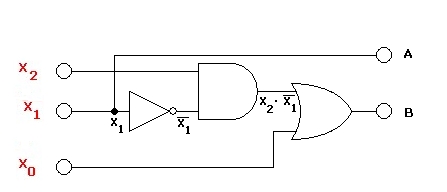

Ecco uno stadio di comparazione :

Alle uscite dei comparatori (sia del primo che secondo stadio di comparazione) abbiamo i segnali Xn, che ci determinano uno Pseudo Bus. Da questo ci prefissiamo di ottenere A e B nel seguente ordine :

| X2 | X1 | X0 | A | B | |

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 | 1 |

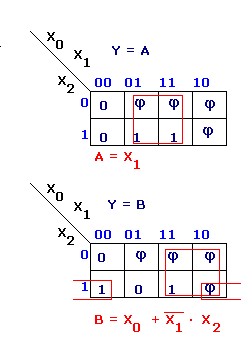

Per ottenere A e B abbiamo bisogno dell'Encoder, quindi si trascrive il tutto come sistema completo a tre variabili con funzioni logiche :

| X2 | X1 | X0 | Y = A | Y = B | |

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 0 | j | j | |

| 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | j | j | |

| 1 | 0 | 1 | j | j | |

| 1 | 1 | 0 | j | j | |

| 1 | 1 | 1 | 1 | 1 |

Alle condizioni dopo dello stadio di comparazione associamo il sistema digitale ordinato a due variabili. Alle altre possibilità per le funzioni A e B abbiamo messo il simbolo j (condizione di indifferenza) che sta per 0 o 1 (in base a come ci fa comodo nella mappa di Karnaught). Ecco le funzioni inserite e sviluppate attraverso le mappe di Karnaught:

da queste ora si ottiene la logica combinatoria , sotto rappresentata che costituisce l'Encoder :

Per avere alla fine la visualizzazione su display si userà un Decoder che avrà il compito di fare accendere i segmenti giusti del display in base a ciò che avrà al suo ingresso (cioè le uscite dell'Encoder).

Il convertitore D/A trasforma una parola digitale fatta di n bit in un livello di tensione. Di conseguenza il numero di livelli di tensione possibili in uscita dal DAC è 2n .

Il segnale analogico fornito dal convertitore D/A non è dunque continuo nel tempo ma è formato da gradini. Ogni gradino corrisponde al valore di tensione associato alla parola

Caratteristiche dei DAC :

La risoluzione è la variazione di tensione dovuta alla variazione di un LSB ed in modo equivalente indica il valore minimo di tensione rappresentabile da un DAC.

La tensione massima di uscita VOM : tale valore si ottiene quando tutti i bit sono a 1.

Setting time è il tempo necessario al DAC per stabilizzarsi al valore finale dell’uscita.

Tipi di DAC :

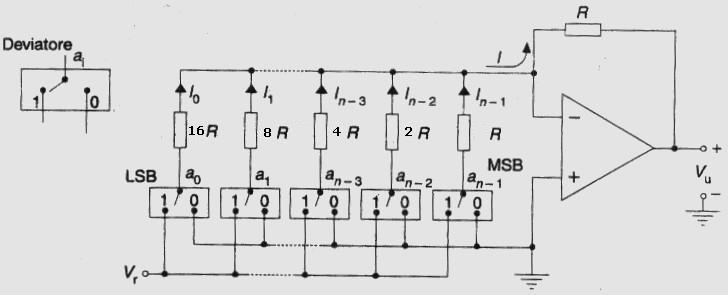

Convertitore a resistenze pesate a 4 bit ; ecco lo schema :

Il circuito è composto da una rete di resistenze, da un convertitore corrente / tensione realizzato con un amplificatore operazionale e da alcuni deviatori. I deviatori sono utili nel nostro caso per descrivere il comportamento del circuito. Nella realtà al posto dei deviatori c’è una rete digitale che fornisce in uscita i livelli di tensione alti e bassi (corrispondenti ai valori logici 1 e 0).

Il numero di resistenze e di deviatori è pari al numero di bit del DAC. Il deviatore consente di collegare la resistenza a massa se il bit vale 0 o al potenziale di riferimento Vr se il bit vale 1. Di conseguenza in ogni resistenza c’è un passaggio di corrente soltanto se il bit associato vale 1 in modo da avere una differenza di potenziale pari a Vr ai capi della stessa resistenza. In caso di bit 0 i due morsetti della resistenza sono a massa e quindi non ci può essere passaggio di corrente.

La corrente che circola in ogni resistenza deve essere tale da dare ad ogni bit il proprio peso in funzione della sua posizione, secondo il principio della conversione. Il valore della corrente deve essere maggiore per il bit più significativo (MSB) per poi diminuire per i bit meno significativi. Si procede dunque collegando al MSB la resistenza minore e raddoppiandone il valore per il bit successivo fino al LSB per il quale la resistenza è 2n-1 volte maggiore rispetto alla prima.

Ad esempio nel caso si DAC a 4 bit: (a3 a2 a1 a0) al bit a3 associamo una resistenza 2R (R è il valore presente nel convertitore corrente/tensione), al bit a2 colleghiamo una resistenza doppia della prima 4R, ad a1 la resistenza 8R ed infine ad a0 la resistenza 16R.

Il convertitore I/V effettua la somma delle correnti, e la tensione in uscita del convertitore è proporzionale al codice d’ingresso.

L’impiego di questi tipo di convertitori DAC è limitato perché presentano alcuni inconvenienti :

- Il valore delle resistenze cresce secondo le potenze del due, fino a raggiungere valori notevoli se il numero di bit del DAC è elevato (RLSB=2nR), non è possibile ovviare a questo problema prendendo un valore di R troppo basso se si vuole garantire un corretto funzionamento dei deviatori elettronici.

- Difficoltà di avere resistenze con valori così diversi e stessa precisione.

- La corrente erogata da Vr dipende dalla combinazione dei bit in ingresso.