# LABORATORIO DI ARCHITETTURA DEI CALCOLATORI lezione n°8

Prof. Rosario Cerbone

rosario.cerbone@libero.it

http://digilander.libero.it/rosario.cerbone

a.a. 2005-2006

### Circuiti Sequenziali

In questa lezione vengono riassunti i concetti fondamentali dei circuiti sequenziali

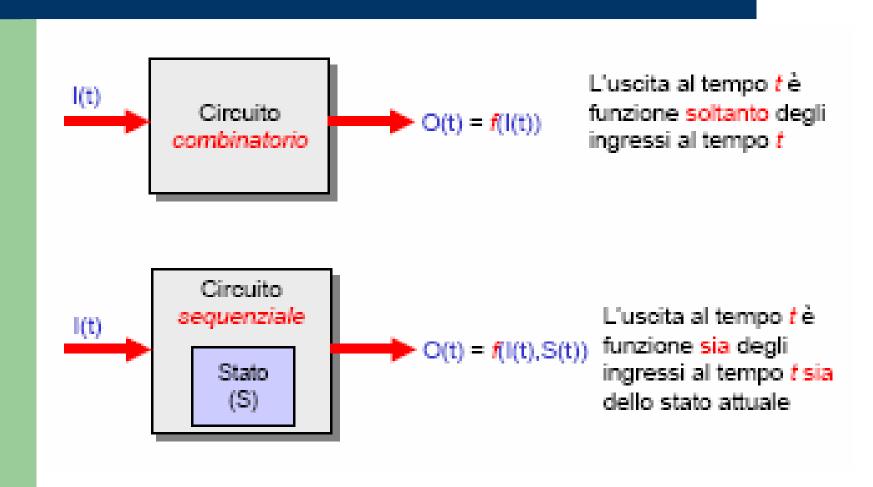

#### Sistemi digitali

- Si possono distinguere due classi di sistemi digitali:

- Sistemi combinatori Il valore delle uscite al generico istante t\* dipende solo dal valore degli ingressi applicati nello stesso istante

- Sistemi sequenziali Il valore delle uscite all'istante t\* dipende non solo dal valore attuale degli ingressi ma anche dalla sequenza di configurazioni d'ingresso precedenti

#### Sistemi Sequenziali - Generalità

- Il comportamento del sistema dipende dalla sua storia precedente

- Sequenziale fa riferimento alla sequenza di eventi che hanno portato il sistema nella sua condizione attuale

- La memoria che il sistema conserva degli eventi passati costituisce lo stato del sistema

#### Sistemi Sequenziali - Generalità

#### **Bistabili - Introduzione**

- Sono elementi di memoria in grado di memorizzare l'informazione binaria relativamente a un singolo evento

- Possono cioè ricordare se all'istante (t-1) il rispettivo ingresso era 0 oppure 1

- Sono quindi elementi sequenziali capaci di mantenersi stabilmente fra due stati (bistabili)

#### Bistabili - Classificazione

- Le differenze principali tra i diversi bistabili dipendono:

- Dal numero di ingressi

- Dal modo in cui tali ingressi ne determinano lo stato

- In generale possono essere classificati

- Asincroni

- Sincroni

#### **Bistabili - Classificazione**

- Asincroni

- E' la variazione di un segnale presente a uno degli ingressi dati che può determinare l'evoluzione del bistabile imponendone il cambiamento di stato

- Hanno solo ingressi dati

- Sincroni

- Le variazioni degli ingressi dati vengono campionate dal segnale presente sull'ingresso di sincronismo, e solo quando tale segnale assume un particolare valore il bistabile può evolvere

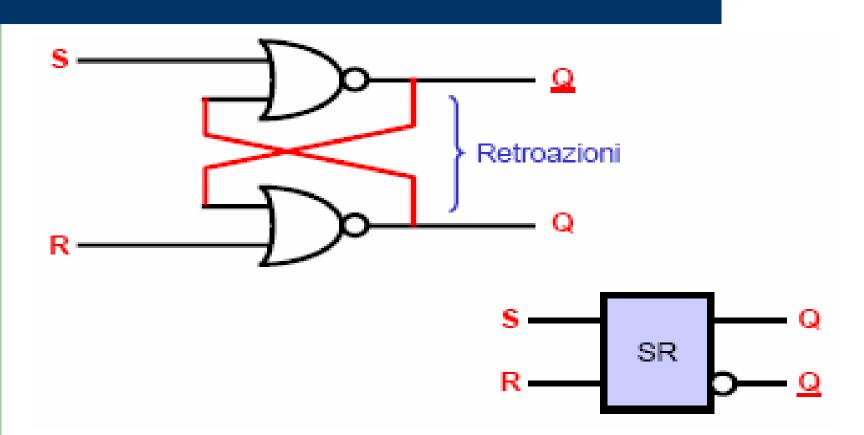

## **Bistabili Asincroni Latch Set-Reset (SR)**

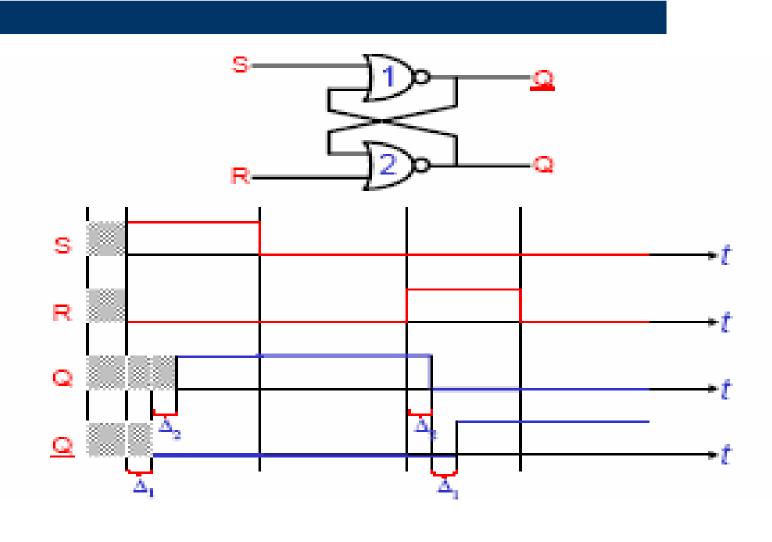

### Bistabili Asincroni Set-Reset (SR) Funzionamento

#### Bistabili Asincroni Set-Reset (SR) Osservazioni

- Q e !Q hanno sempre valori complementari

- L'effetto di un 1 su S (set) è di portare a 1 l'uscita Q

- L'effetto di un 1 su R (Reset) è di portare a 0 l'uscita Q

- La presenza di un 1 sia su S che su R provoca un comportamento che non rispetta più quanto osservato:

- Le due uscite tendono ad assumere lo stesso valore

- La commutazione delle uscite diventa imprevedibile:

- dipende dalle relazioni tra i ritardi distribuiti lungo i vari percorsi

- Si impone che la configurazione di ingresso 11 non possa mai verificarsi

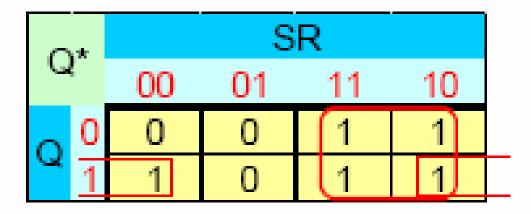

### Bistabili Asincroni - Latch Set-Reset (SR) Tabella delle transizioni

- La Tabella delle Transizioni consente di descrivere il comportamento di un bistabile

- Simbologia

- Indicheremo con Q\* lo stato prossimo

| Q* |   | SR |    |    |    |  |  |

|----|---|----|----|----|----|--|--|

|    |   | 00 | 01 | 11 | 10 |  |  |

| Q  | 0 | 0  | 0  | Χ  | 1  |  |  |

|    | 1 | 1  | 0  | Χ  | 1  |  |  |

#### Bistabili Asincroni - Latch Set-Reset (SR) Equazione di funzionamento

- La configurazione SR=11 la possiamo vedere come una condizione di indifferenza visto che è una configurazione che non dovrà mai presentarsi e per la quale quindi l'uscita non sarà mai presa in considerazione

- Possiamo quindi scrivere l'equazione di funzionamento del bistabile SR

- Riduciamo la Q\*(S,R,Q) utilizzando le mappe di Karnaugh

$$Q^*(S,R,Q) = S + RQ$$

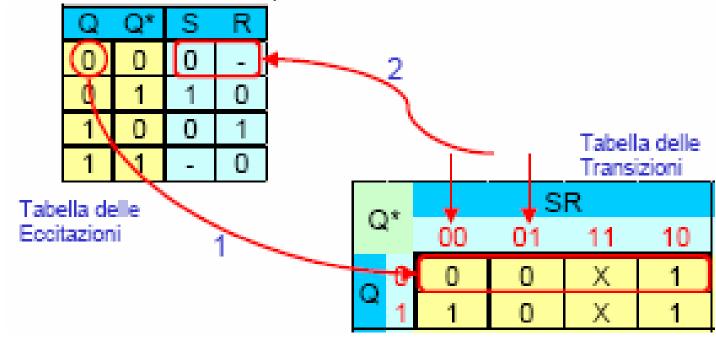

### Bistabili Asincroni - Latch Set-Reset (SR) Tabella delle Eccitazioni

- La Tabella delle Eccitazioni consente di conoscere la configurazione degli ingressi da applicare affinché possa avvenire una certa transizione di stato

- Può essere ricavata a partire dalla Tabella delle transizioni

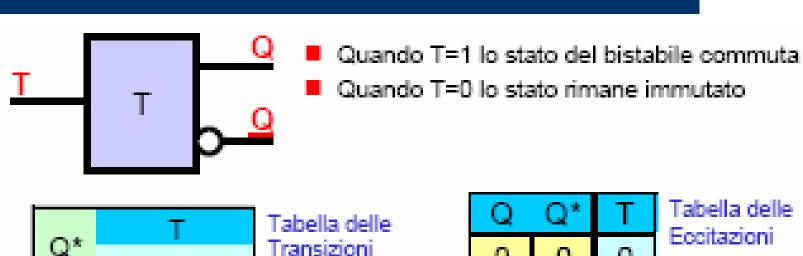

#### Bistabili Asincroni Triggered o Toggle (T)

| Q* |   | Т |   |  |

|----|---|---|---|--|

|    |   | 0 | 1 |  |

| _  | 0 | 0 | 1 |  |

| Q  | 1 | 1 | 0 |  |

a delle 0 0 0 0 0 0 1 1 1 1 0 1

$$Q^*(T,Q) = TQ + QT$$

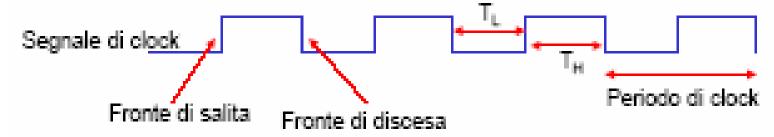

#### **Sincronia**

- Un bistabile asincrono modifica il proprio stato solo in presenza di un evento sugli ingressi

- Il progetto delle reti può richiedere che il cambiamento avvenga in istanti di tempo ben precisi

- Questa esigenza impone la presenza di un segnale di ingresso di controllo

- Il segnale che prendiamo in considerazione è periodico, detto segnale di clock

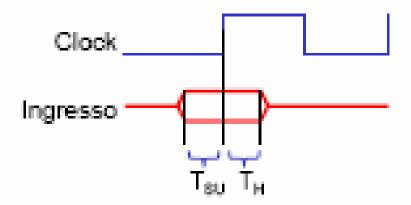

#### Tempi di Hold e di Set-up

- Affinché venga riconosciuto correttamente, un ingresso deve rimanere stabile in una finestra temporale nell'intorno di un fronte del clock

- Tempo di *Set-up* (TSU)

- Minimo intervallo di tempo che precede il fronte del clock durante il quale l'ingresso deve essere mantenuto stabile

- Tempo di Hold (TH)

- Minimo intervallo di tempo che segue il fronte del clock durante il quale l'ingresso deve essere mantenuto stabile

#### **Bistabili Sincroni**

- Le variazioni degli ingressi dati vengono campionate dal segnale presente sull'ingresso di sincronismo, e solo quando tale segnale assume un particolare valore il bistabile può evolvere

- Latch Trasparente Sincrono

- Quando il segnale di sincronismo è attivo, l'effetto di una variazione di un valore presente sugli ingressi dati si riflette immediatamente nel valore dello stato (e, quindi, dell'uscita) del latch

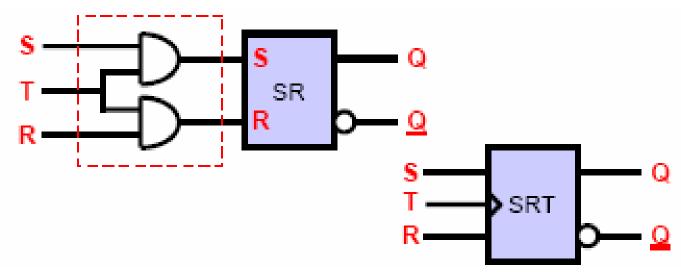

#### Bistabili Sincroni Bistabile SRT

Si ottiene dal latch SR aggiungendo la logica necessaria ad abilitarlo (renderlo trasparente) soltanto su attivazione di un segnale di sincronismo T

### Bistabili Sincroni - Bistabile SRT Funzionamento

- Quando il segnale di sincronismo è attivo (intervallo di trasparenza), il bistabile si comporta come l'SR

- Quando il segnale di sincronismo non è attivo, il bistabile mantiene immutato il proprio stato

| _  | en e | SR |    |    |    |   |

|----|------|----|----|----|----|---|

| Q× |      | 00 | 01 | 11 | 10 | T |

|    | 00   | 0  | 0  | 0  | 0  |   |

| οт | 01   | 0  | 0  | X  | 1  |   |

| ÿ  | 11   | 1  | 0  | Х  | 1  |   |

|    | 10   | 1  | 1  | 1  | 1  |   |

Tabella delle Transizioni

> La tabella delle eccitazioni è identica a quella del latch SR se si considera il funzionamento negli intervalli di trasparenza

$$Q^*(S,R,Q,T) = QT + ST + RQ = ST + Q(R + T)$$

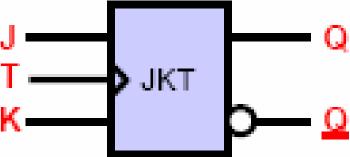

#### Bistabili Sincroni Bistabile JKT - Funzionamento

- La condizione che ai due ingressi S ed R non siano mai contemporaneamente presenti due 1 può complicare il progetto della rete nella quale inserire il bistabile

- Il bistabile JKT risolve questa condizione

- Quando il segnale di sincronismo non è attivo, il bistabile mantiene immutato il proprio stato

- Quando il segnale di sincronismo è attivo

- Se i due ingressi sono diversi o entrambi uguali a 0, si comporta come l'SR (in cui J→S, K→R)

- Se i due ingressi sono entrambi uguali a 1 lo stato del bistabile commuta

### Bistabili Sincroni JKT Tabelle ed Equazioni

| _  | æ  | JK |    |    |    |  |

|----|----|----|----|----|----|--|

| Q× |    | 00 | 01 | 11 | 10 |  |

|    | 00 | 0  | 0  | 0  | 0  |  |

| ОΤ | 01 | 0  | 0  | 1  | 1  |  |

| ΨI | 11 | 1  | 0  | 0  | 1  |  |

|    | 10 | 1  | 1  | 1  | 1  |  |

Tabella delle Transizioni

| Q | $\mathbb{Q}^{z}$ | J | K |

|---|------------------|---|---|

| 0 | 0                | 0 | - |

| 0 | 1                | 1 | • |

| 1 | 0                | - | 1 |

| 1 | 1                | - | 0 |

Tabella delle Eccitazioni

$$Q^*(J,K,Q,T) = QT + JQT + KQ = Q(T + K) + JQT$$

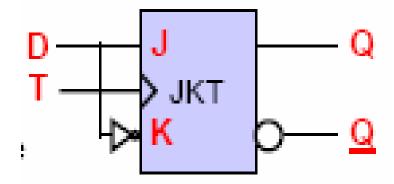

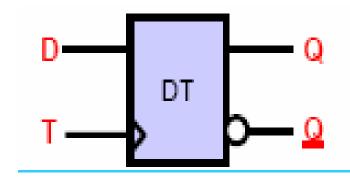

#### Bistabili Sincroni Bistabile DT - Funzionamento

- Il bistabile DT (D sta per Data) è molto usato nella sintesi delle reti sequenziali

- Si ottiene dal JK ponendo J→D e K→!D

- Il funzionamento è molto semplice

- Quando il segnale di sincronismo è attivo all'uscita del bistabile si trasferisce il valore presente sull'ingresso D

- Quando il segnale di sincronismo non è attivo il valore dell'uscita Q non cambia (mantiene lo stato)

#### Bistabili Sincroni Bistabile DT - Tabelle ed Equazioni

| Q* |   | DT |    |    |    |  |

|----|---|----|----|----|----|--|

|    |   | 00 | 01 | 11 | 10 |  |

| Ø  | 0 | 0  | 0  | 1  | 0  |  |

|    | 1 | 1  | 0  | 1  | 1  |  |

Tabella delle Transizioni

| Q | Q* | D |

|---|----|---|

| 0 | 0  | 0 |

| 0 | 1  | 1 |

| 1 | 0  | 0 |

| 1 | 1  | 1 |

Tabella delle Eccitazioni

$$Q^*(D,T,Q) = DT + \underline{T}Q$$

#### Segnale di Reset

- In molti casi è necessario poter forzare il bistabile (sincrono o asincrono) in uno stato predeterminato indipendente dai valori di ingresso

- Ciò per garantire che nell'istante iniziale in cui si fornisce alimentazione al circuito, i bistabili in esso presenti si portino in uno stato iniziale noto

- Per questo i bistabili possono essere dotati di un ingresso asincrono di reset

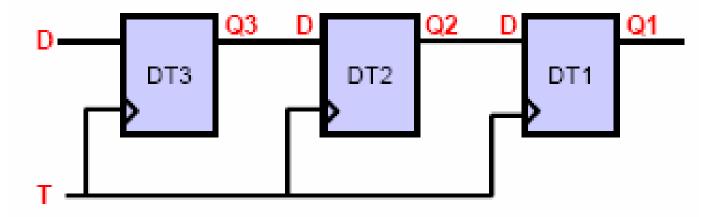

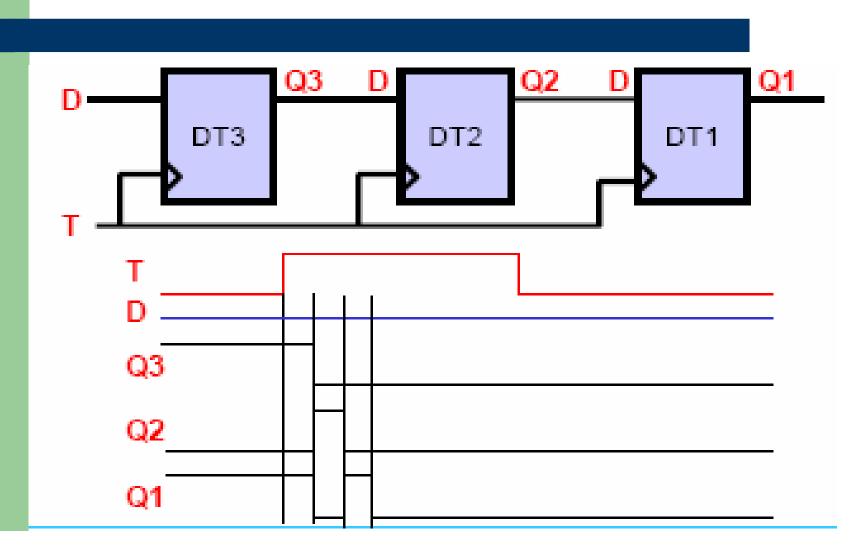

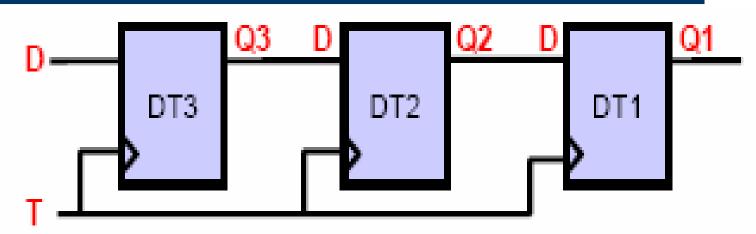

#### **Bistabili Master-Slave Slave**

- Spesso per garantire il buon funzionamento di una rete sequenziale, i bistabili di tipo *latch trasparenti sincroni* non hanno un comportamento soddisfacente

- Es.: Registro a scorrimento basato su bistabili DT

#### **Bistabili Master-Slave**

#### **Bistabili Master-Slave**

Stato Iniziale 101 (Q<sub>3</sub>Q<sub>2</sub>Q<sub>1</sub>)

T=1 per un tempo  $\Delta$ , D=0

Stato successivo: 000 ( $Q_3Q_2Q_1$ )

#### Conclusione

In dipendenza dai valori relativi dei ritardi interni del bistabile e del segnale di sincronismo, il comportamento non è quello corretto e può essere imprevedibile

#### **Edge-Sensitive Flip-Flop**

- Per ovviare ai problemi suddetti sono stati introdotti i bistabili con memoria ausiliaria

- Tali bistabili rispondono al fronte del segnale di sincronismo e non al livello

- Si parla di

- configurazioni Master-Slave

- Edge-Sensitive

- Edge-Triggered

- Edge-Sensitive flip-flop

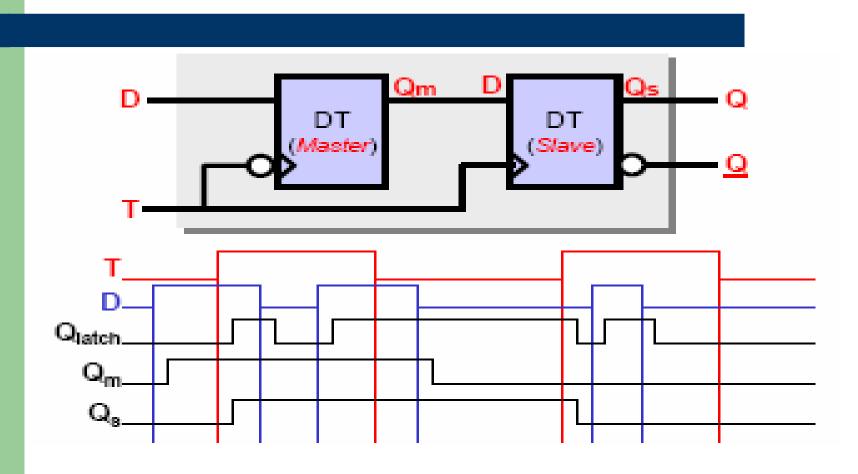

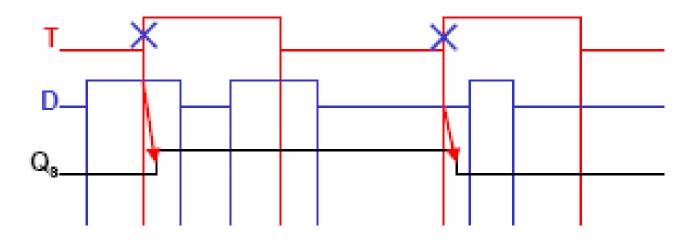

#### **Bistabile Master-Slave DT**

#### **Bistabile Master-Slave DT**

Nella configurazione Master-Slave del bistabile DT l'ingresso si trasferisce all'uscita sul fronte di salita del segnale di sincronismo

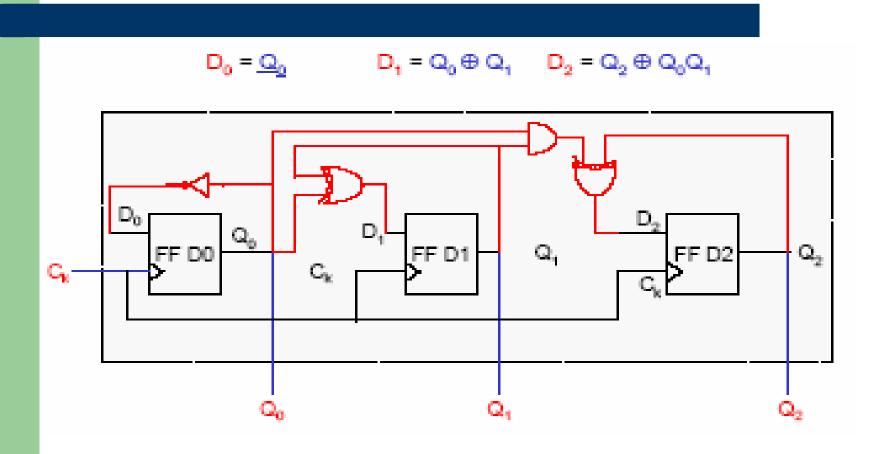

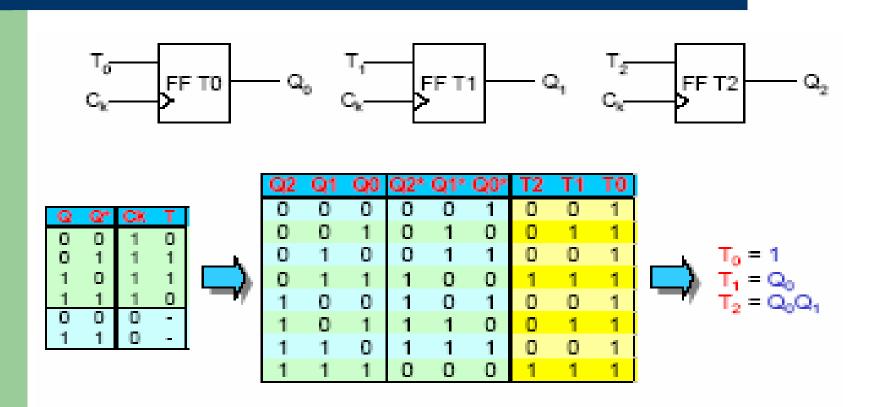

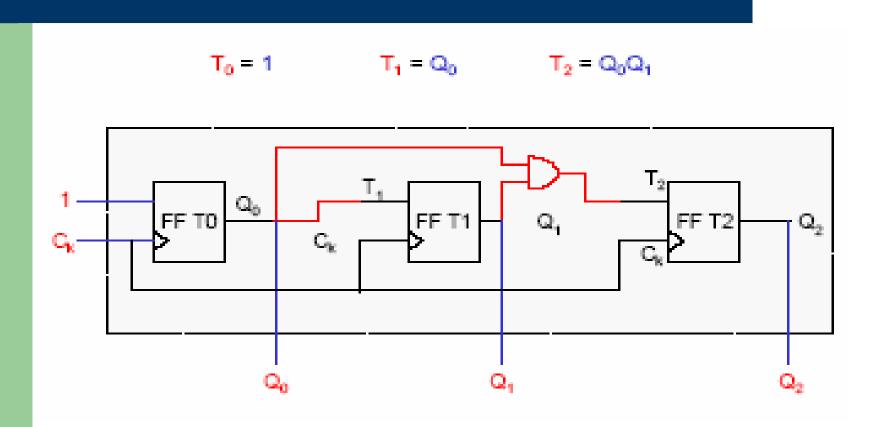

#### Contatori Sincroni Contatori Modulo 8 con FF T

#### Contatori Sincroni Contatori Modulo 8 con FF T

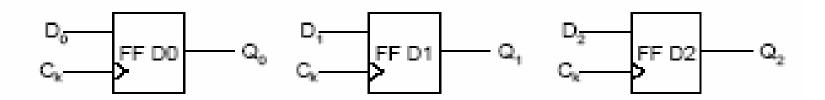

#### Contatori Sincroni Contatori Modulo 8 con FF D

| G | G* | Ck | D |

|---|----|----|---|

| 0 | Ð  | 1  | 0 |

| 0 | 1  | 1  | 1 |

| 1 | 0  | 1  | 0 |

| 1 | 1  | 1  | 1 |

| 0 | Ģ  | 0  | - |

| 1 | 1  | 0  | - |

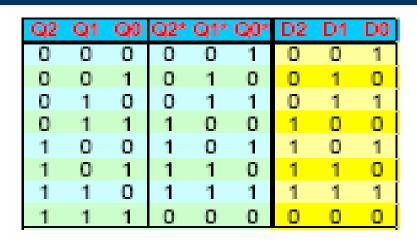

| Q2 | Q1 | Q0 | Q2* | Q1* | Q0* | D2 | D1 | DO |

|----|----|----|-----|-----|-----|----|----|----|

| 0  | 0  | 0  | 0   | 0   | -   | 0  | 0  | 1  |

| 0  | 0  | 1  | 0   | 1   | 0   | 0  | 1  | 0  |

| 0  | 1  | 0  | 0   | 1   | 1   | 0  | 1  | 1  |

| 0  | 1  | 1  | 1   | 0   | 0   | 1  | 0  | 0  |

| 1  | 0  | 0  | 1   | 0   | 1   | 1  | 0  | 1  |

| 1  | 0  | 1  | 1   | 1   | 0   | 1  | 1  | 0  |

| 1  | 1  | 0  | 1   | 1   | 1   | 1  | 1  | 1  |

| 1  | 1  | 1  | 0   | 0   | 0   | 0  | 0  | 0  |

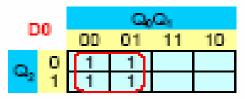

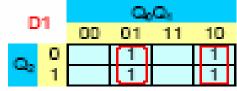

#### Contatori Sincroni Contatori Modulo 8 con FF D

$$D_0 = \Omega_0$$

$$D_1 = \underline{Q_0}Q_1 + Q_0\underline{Q_1} = Q_0 \oplus Q_1$$

$$D_2 = C_0C_1\underline{C}_2 + \underline{C}_0C_2 + \underline{C}_1C_2 = C_2 \oplus C_0C_1$$

#### Contatori Sincroni Contatori Modulo 8 con FF D