Un

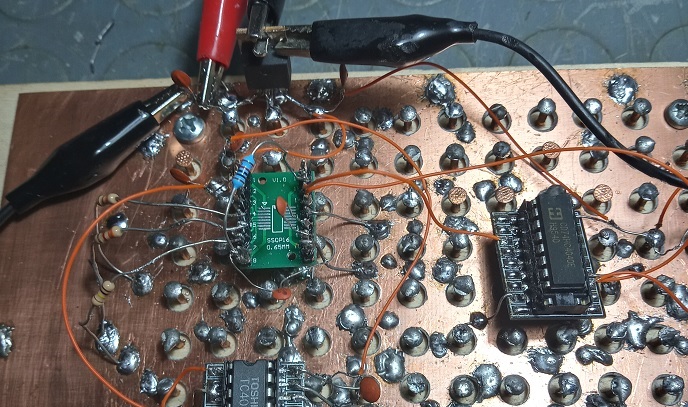

mio amico mi ha chiesto se potevo costruirgli un oscillatore a

frequenza costante di 21.333 MHz che gli sarebbe poi servito per

effettuare delle prove su delle RAM e così ho fatto. Il circuito è

molto semplice, esso è composto da due divisori (74HC4018 e 74HC4040) e

dall'integrato 74HC4046 (l'integrato è saldato sotto la schedina),

questo è un PLL, al suo interno c'è un VCO e tre comparatori di fase

per soddisfare ogni richiesta del progettista. La frequenza del VCO è

determinata dalle resistenze R1, R2 e dal condensatore C2, la massima

frequenza che può generare il VCO senza il condensatore C2 e con R1 e

R2 pari a 3K3, si aggira attorno ai 30 MHz. Comunque per una buona

stabilità in frequenza il costruttore consiglia di usare condensatori

di valore non inferiore ai 40 pF e per una buona linearità del

guadagno del VCO di non usare resistenze inferiore ai 3K. Io ho

utilizzato due resistenze da 3K3 ed un condensatore da 40 pF, in questo

modo il VCO oscilla in free-run ad una frequenza molto vicina ai

21 MHz con una tensione di controllo sul pin 9 di 2.5V (metà

tensione di alimentazione).

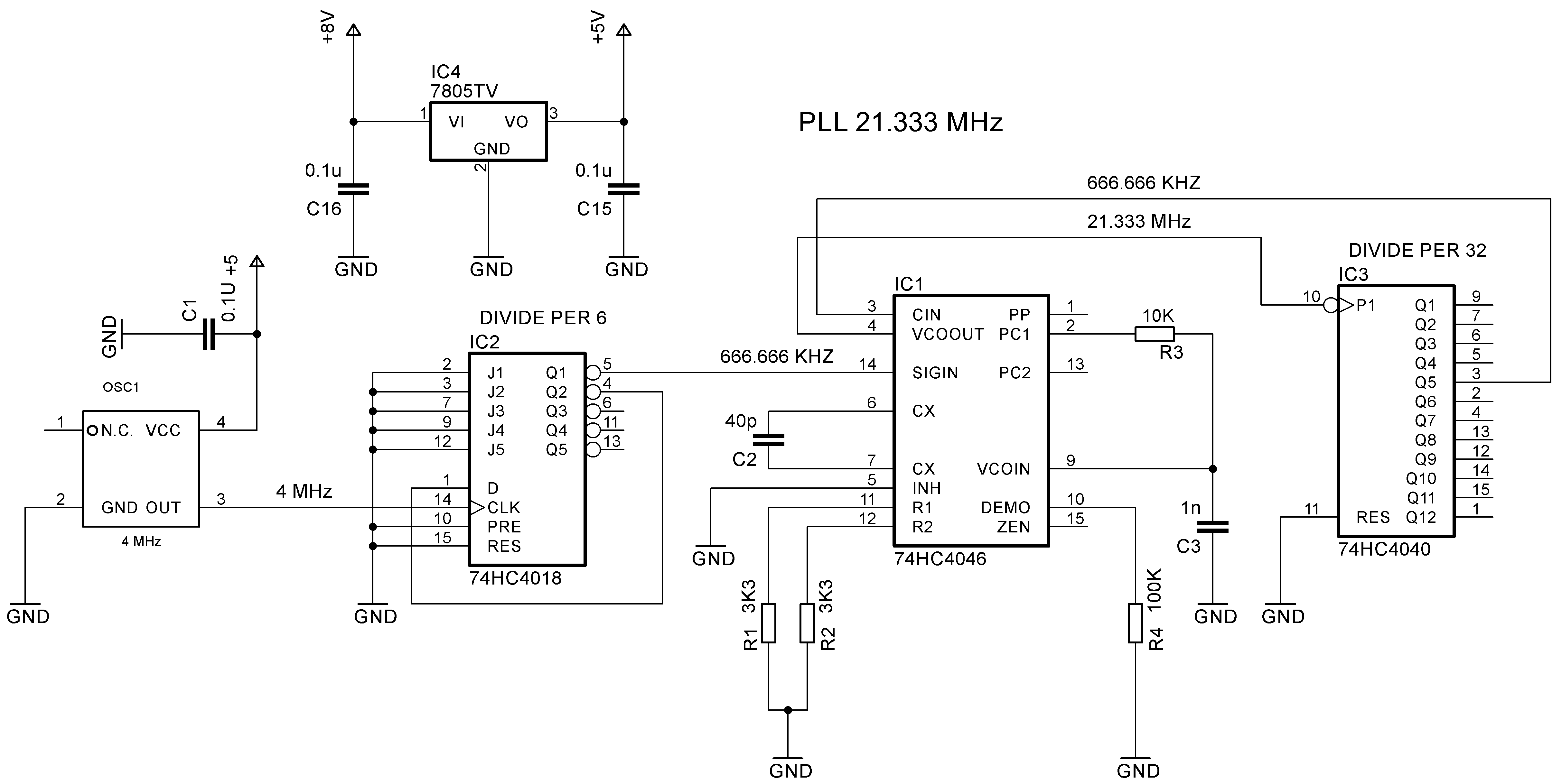

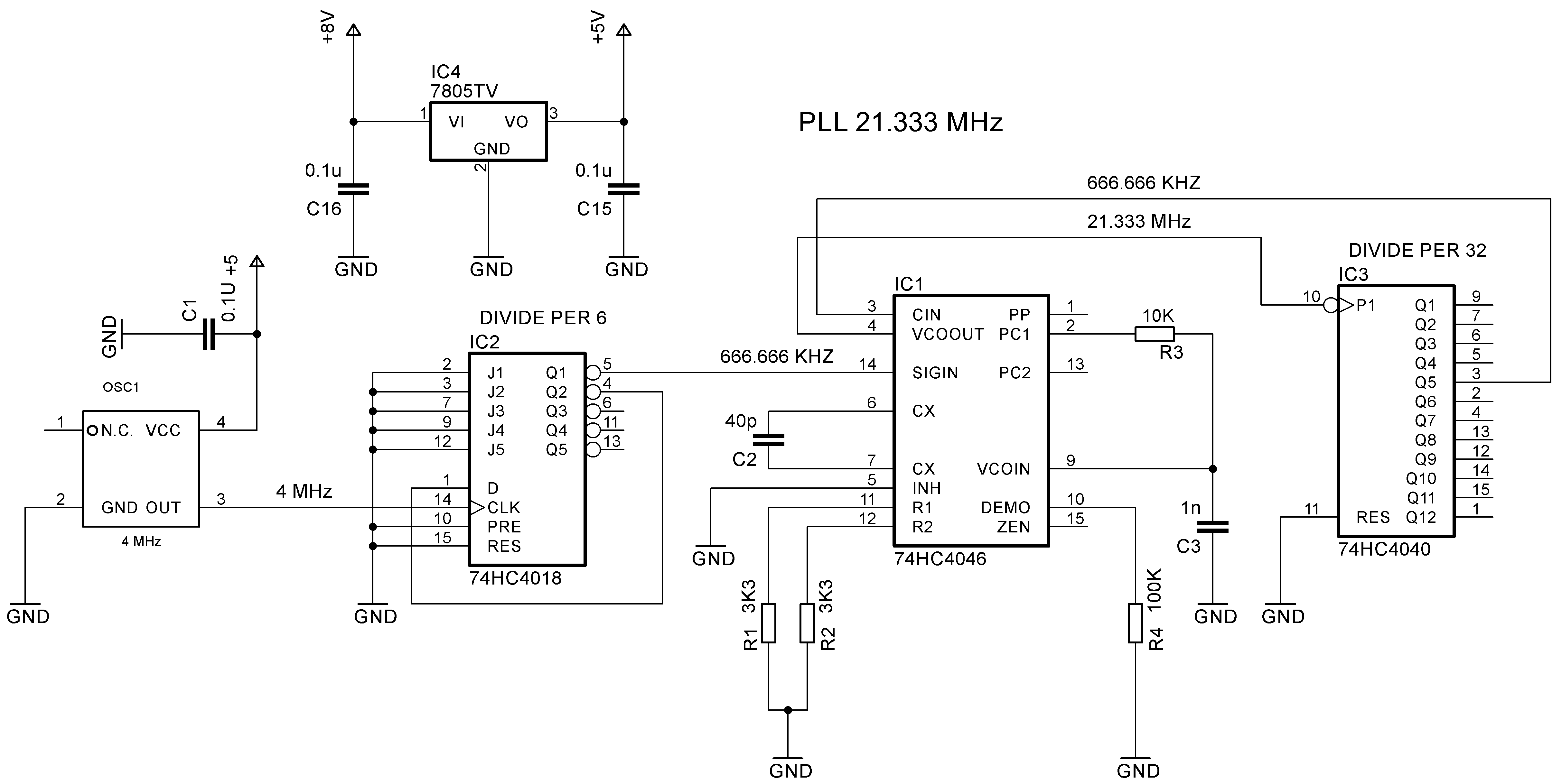

Lo schema è il seguente:

Il segnale di riferimento è generato da un oscillatore da 4 MHz (OSC1) e diviso per 6 da IC2, questo segnale viene inviato ad un ingresso del comparatore di fase (SIGIN). La frequenza del segnale all'uscita del VCO (VCOOUT) viene divisa da IC3 la cui uscita è collegata all'altro ingresso del comparatore di fase (CIN). Quando il PLL è in lock le frequenze dei due segnali applicati agli ingressi del comparatore sono uguali e i segnali stessi sfasati tra di loro di circa 90°. In queste condizioni la tensione all'ingresso del VCO (VCOIN) è di 2.65V.

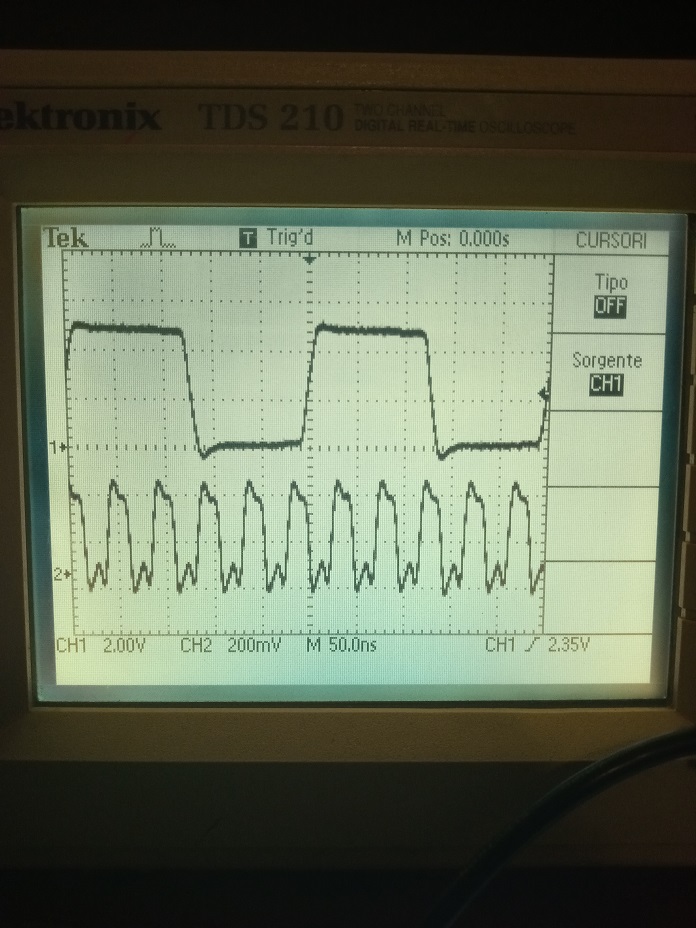

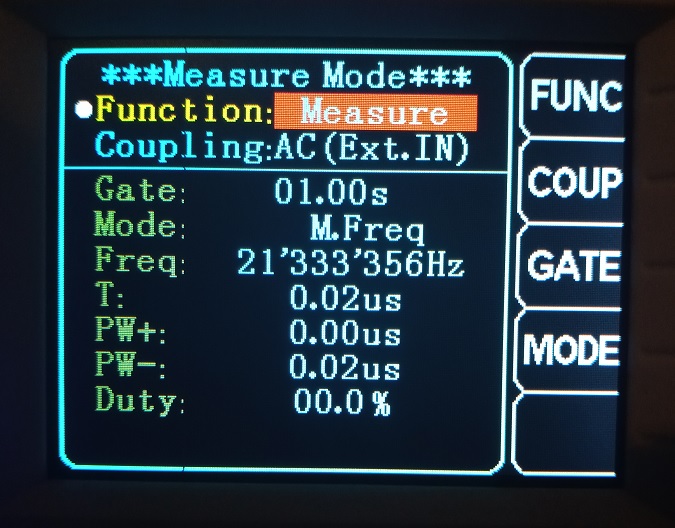

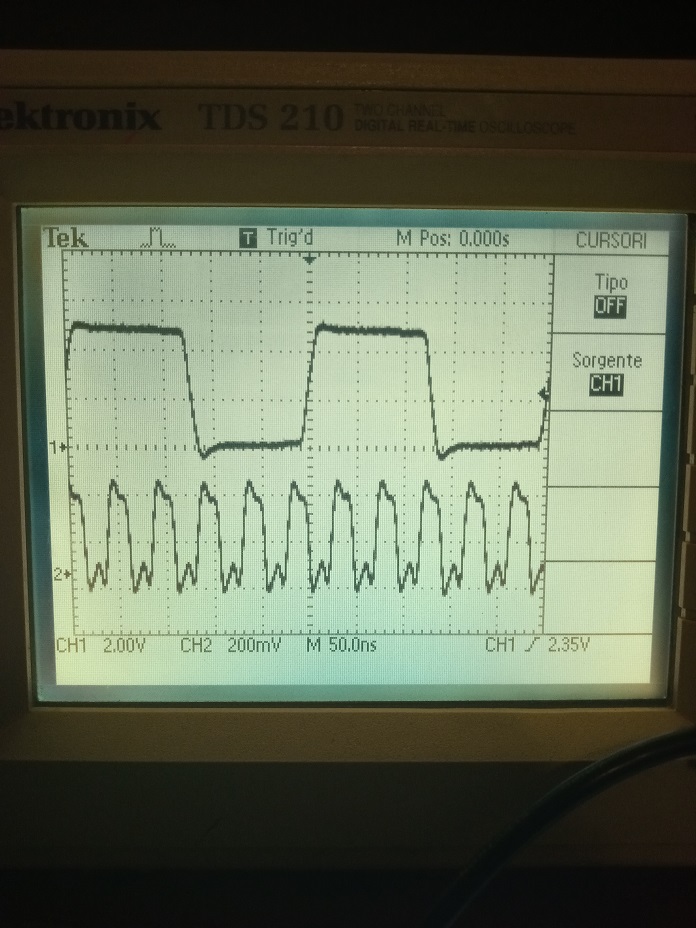

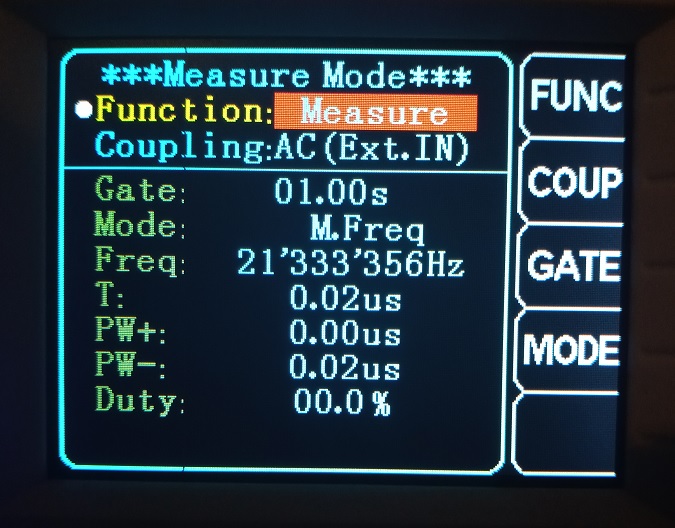

Qui di seguito il segnale a 21.333 MHz agganciato a quello di riferimento di 4 MHz e la lettura del frequenzimetro.

Fabio

Lo schema è il seguente:

Il segnale di riferimento è generato da un oscillatore da 4 MHz (OSC1) e diviso per 6 da IC2, questo segnale viene inviato ad un ingresso del comparatore di fase (SIGIN). La frequenza del segnale all'uscita del VCO (VCOOUT) viene divisa da IC3 la cui uscita è collegata all'altro ingresso del comparatore di fase (CIN). Quando il PLL è in lock le frequenze dei due segnali applicati agli ingressi del comparatore sono uguali e i segnali stessi sfasati tra di loro di circa 90°. In queste condizioni la tensione all'ingresso del VCO (VCOIN) è di 2.65V.

Qui di seguito il segnale a 21.333 MHz agganciato a quello di riferimento di 4 MHz e la lettura del frequenzimetro.

Fabio