Un'accozzaglia

di componenti distanti tra loro decine di centimetri collegati con fili

volanti che si sormontano l'un l'altro, reofori lunghi e alcuni

integrati senza condensatore di by-pass sull'alimentazione...eppur funziona.

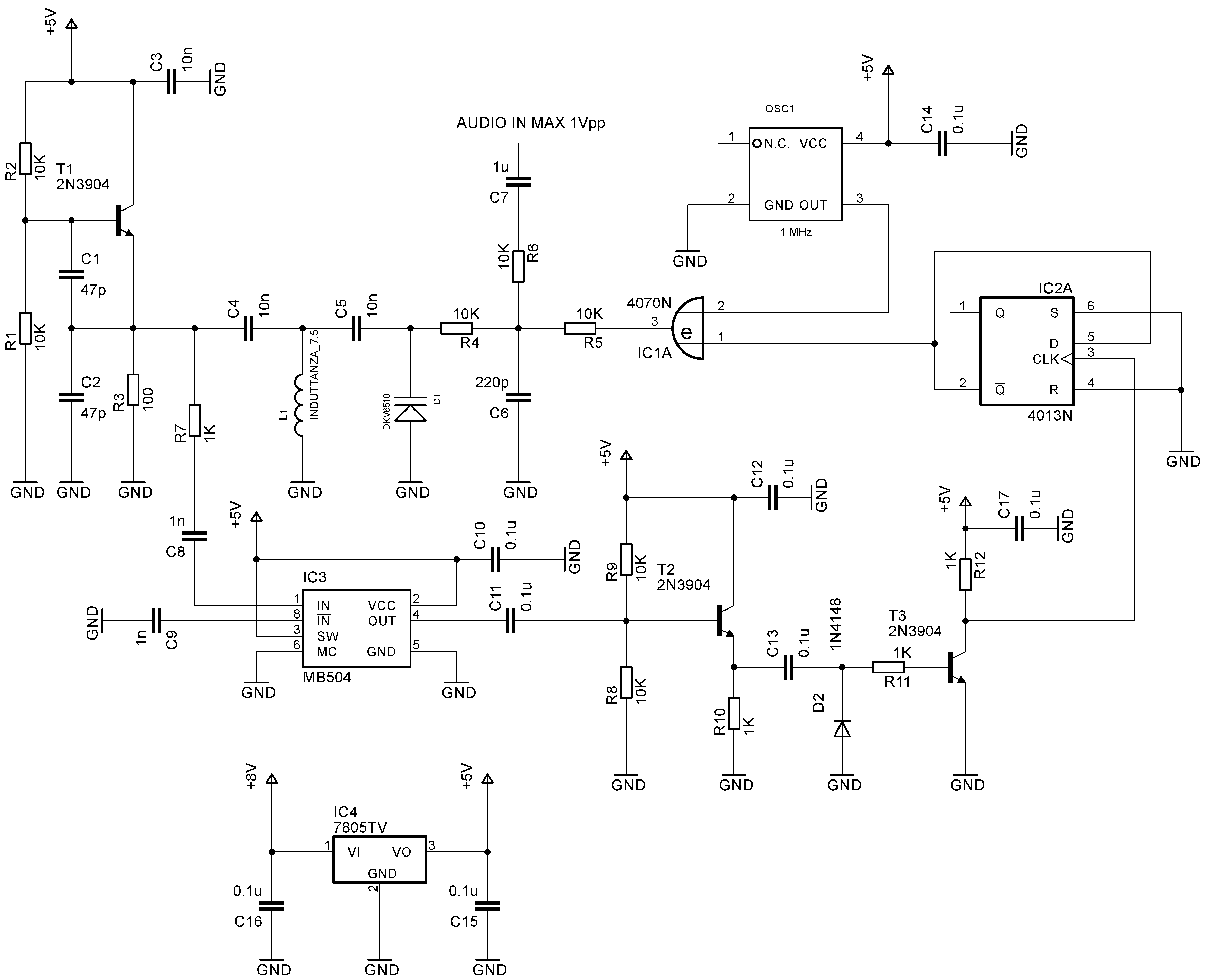

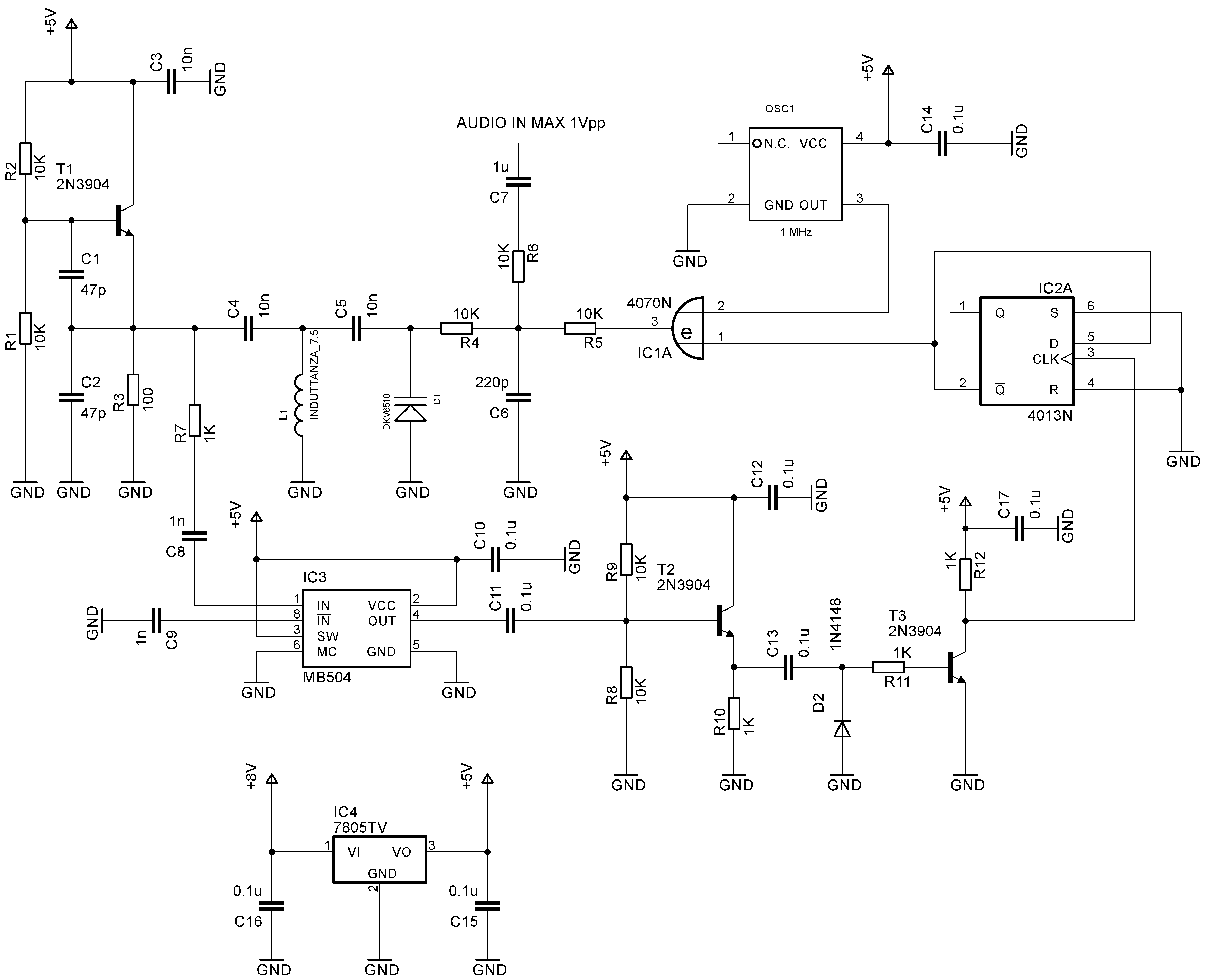

Desideravo ottenere da questo circuito un segnale sinusoidale rigorosamente costante a 66 MHz e ci sono riuscito anche se dopo diversi tentativi, il circuito nel suo complesso è un PLL; con un segnale di riferimento a frequenza di 1 MHz stabile si ottiene un segnale a 66 MHz anch'esso stabile, il tutto con una manciata di componenti. Nella figura seguente è visualizzato lo schema elettrico:

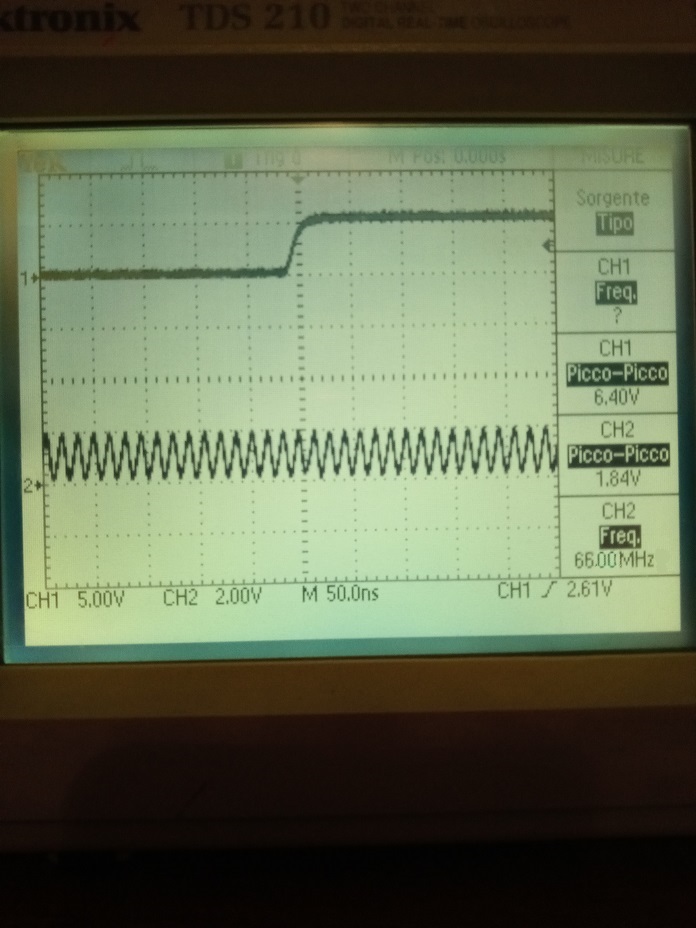

La descrizione inizierà proprio dal segnale generato, per questa si farà uso di immagini sulle quali sono visualizzati i diversi segnali da analizzare. La prima rappresenta:

- Il segnale di riferimento prelevato con la sonda direttamente sul terminale di uscita dell'oscillatore quarzato; questo segnale è visualizzato sul canale 1 dell'oscilloscopio (quello in alto), per tutte le foto che seguiranno questo segnale sarà sempre presente su quello stesso canale.

- Il segnale a 66 MHz prelevato sul collettore di T1 visualizzato sul canale 2 dell'oscilloscopio.

Si nota subito dalla lettura della frequenza la precisione della stessa; 66.00 MHz esatti, la frequenza del il segnale di riferimento non può essere letta dall'oscilloscopio dato che ho allargato oltre il periodo del segnale stesso la scala dei tempi. Questo l'ho dovuto fare per vedere un certo numero di sinusoidi a 66 MHz.

Il VCO è un Colpitts e la frequenza è controllata dal diodo varicap D1. Ho dimensionato i componenti passivi affinché senza il segnale di riferimento il VCO oscilli ad una frequenza vicino a 66 MHz quando ai capi del diodo varicap è presente una tensione di 2.5 V, questo per far lavorare il comparatore di fase vicino il centro della sua possibilità quando il sistema è agganciato (cioè la tensione continua si discosta di poco da quel valore con 66 MHz esatti).

Il segnale generato viene prelevato dall'emettitore di T1 e tramite R7 C8 inviato all'ingresso del prescaler IC3, questo integrato è programmato per dividere per 33, esso accetta segnali di tutte le forme d'onda con livello compreso tra 100 mVpp a 800 mVpp, se il livello d'ingresso esce da questi due valori il prescaler divide per numeri casuali diversi da 33. Il livello di uscita di questo integrato è molto basso (circa 2 Vpp appoggiati su una continua) non adatto a pilotare CMOS, inoltre la corrente che esso può erogare non supera un paio di mA senza che si pregiudichi la forma d'onda, occorre quindi inserire due transistor per potergli far pilotare l'integrato IC2.

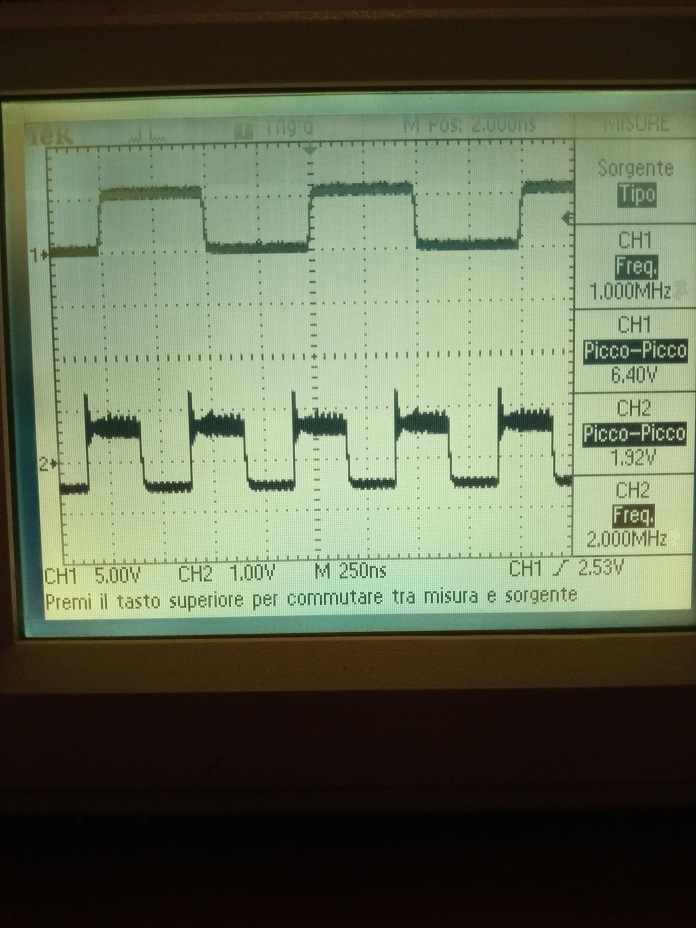

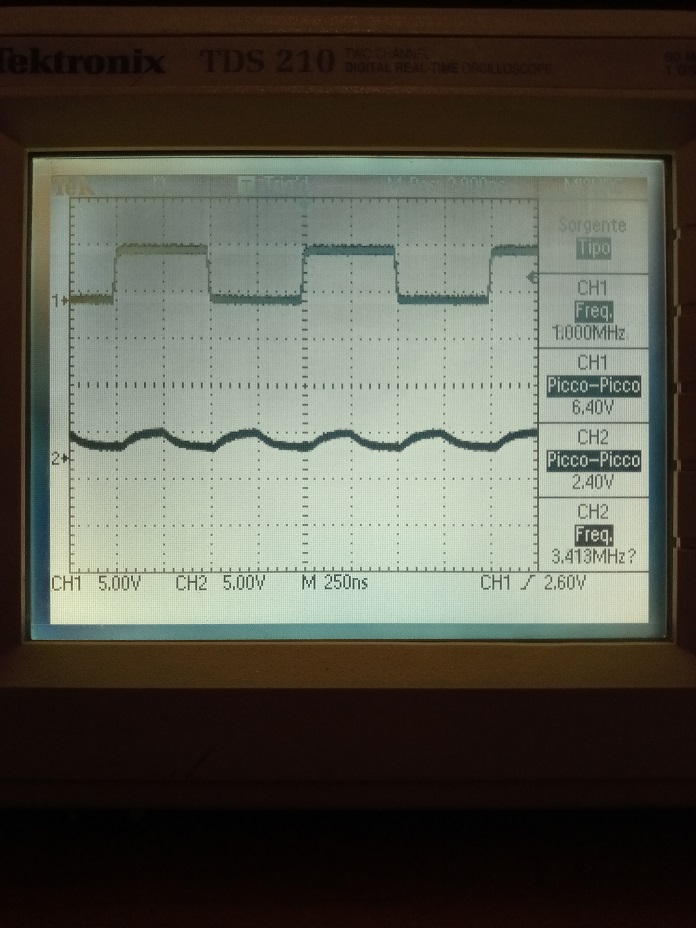

Nella foto successiva è visualizzato:

- Sul canale 1 sempre il segnale di riferimento.

- Sul canale 2 il segnale presente sul diodo D2.

Si noti la frequenza a 2 MHz (66 MHz / 33). Il segnale prelevato sul collettore di T3 è inviato all'ingresso clock del flip-flop IC2 che divide per due la frequenza in ingresso, nella foto successiva è visualizzato:

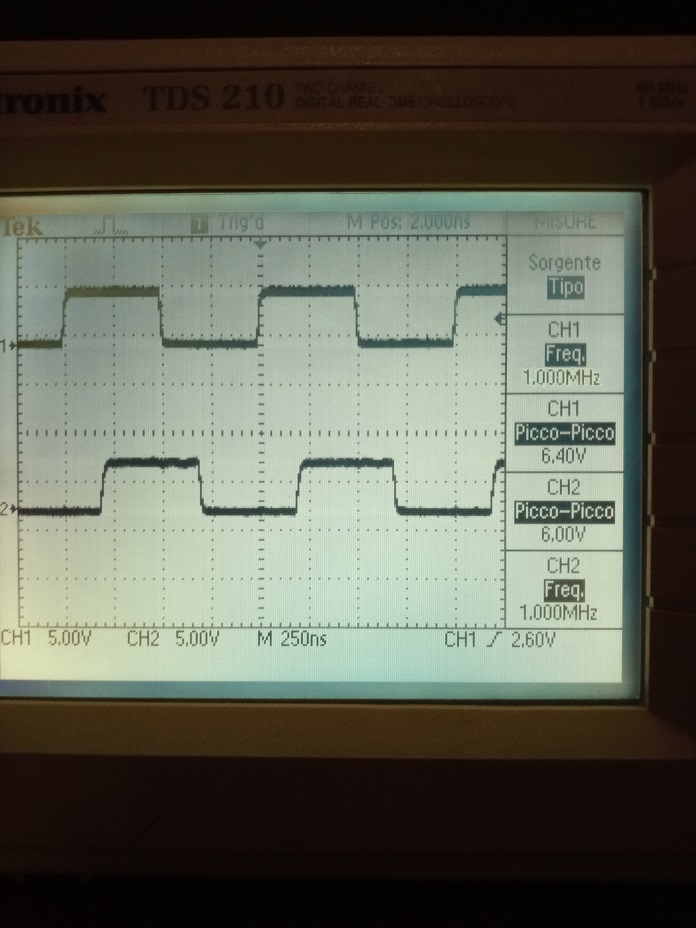

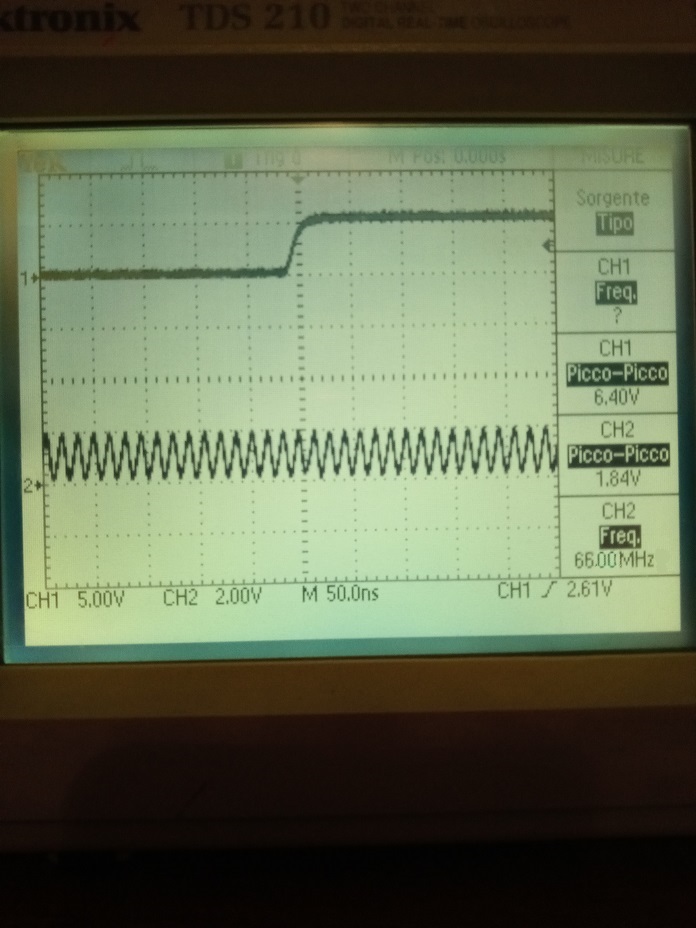

- Sul canale 1 sempre il segnale di riferimento.

- Sul canale 2 il segnale presente sul pin 2 e 5 di IC2.

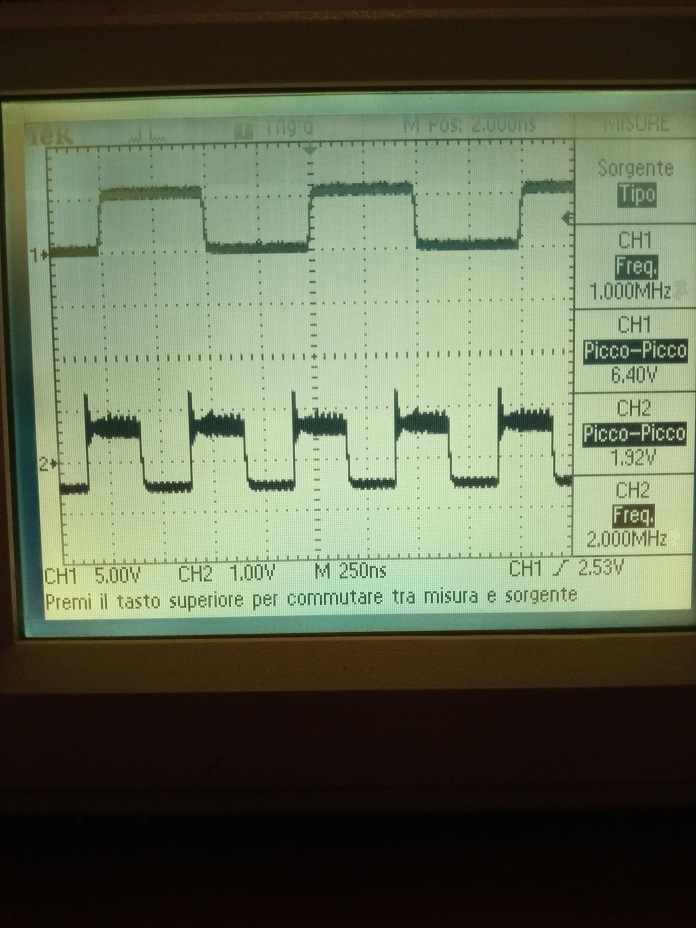

Si noti che ora i segnali hanno la stessa frequenza ma sono sfasati di circa 90°, condizione di aggancio per un valore di tensione continua ai capi del diodo varicap di circa 2.5V. Nella foto successiva viene visualizzato:

- Sul canale 1 sempre il segnale di riferimento.

- Sul canale 2 il segnale presente ai capi di C6.

Il valore della tensione continua ai capi di C6 è 2.25V.

Il circuito è semplice ma mantiene la frequenza a 66 MHz rigorosamente costante. Per poter verificare questa costanza ho tenuto in funzione il PLL per diverse ore monitorandolo con un ricevitore FM.

Ciao.

Fabio

Desideravo ottenere da questo circuito un segnale sinusoidale rigorosamente costante a 66 MHz e ci sono riuscito anche se dopo diversi tentativi, il circuito nel suo complesso è un PLL; con un segnale di riferimento a frequenza di 1 MHz stabile si ottiene un segnale a 66 MHz anch'esso stabile, il tutto con una manciata di componenti. Nella figura seguente è visualizzato lo schema elettrico:

La descrizione inizierà proprio dal segnale generato, per questa si farà uso di immagini sulle quali sono visualizzati i diversi segnali da analizzare. La prima rappresenta:

- Il segnale di riferimento prelevato con la sonda direttamente sul terminale di uscita dell'oscillatore quarzato; questo segnale è visualizzato sul canale 1 dell'oscilloscopio (quello in alto), per tutte le foto che seguiranno questo segnale sarà sempre presente su quello stesso canale.

- Il segnale a 66 MHz prelevato sul collettore di T1 visualizzato sul canale 2 dell'oscilloscopio.

Si nota subito dalla lettura della frequenza la precisione della stessa; 66.00 MHz esatti, la frequenza del il segnale di riferimento non può essere letta dall'oscilloscopio dato che ho allargato oltre il periodo del segnale stesso la scala dei tempi. Questo l'ho dovuto fare per vedere un certo numero di sinusoidi a 66 MHz.

Il VCO è un Colpitts e la frequenza è controllata dal diodo varicap D1. Ho dimensionato i componenti passivi affinché senza il segnale di riferimento il VCO oscilli ad una frequenza vicino a 66 MHz quando ai capi del diodo varicap è presente una tensione di 2.5 V, questo per far lavorare il comparatore di fase vicino il centro della sua possibilità quando il sistema è agganciato (cioè la tensione continua si discosta di poco da quel valore con 66 MHz esatti).

Il segnale generato viene prelevato dall'emettitore di T1 e tramite R7 C8 inviato all'ingresso del prescaler IC3, questo integrato è programmato per dividere per 33, esso accetta segnali di tutte le forme d'onda con livello compreso tra 100 mVpp a 800 mVpp, se il livello d'ingresso esce da questi due valori il prescaler divide per numeri casuali diversi da 33. Il livello di uscita di questo integrato è molto basso (circa 2 Vpp appoggiati su una continua) non adatto a pilotare CMOS, inoltre la corrente che esso può erogare non supera un paio di mA senza che si pregiudichi la forma d'onda, occorre quindi inserire due transistor per potergli far pilotare l'integrato IC2.

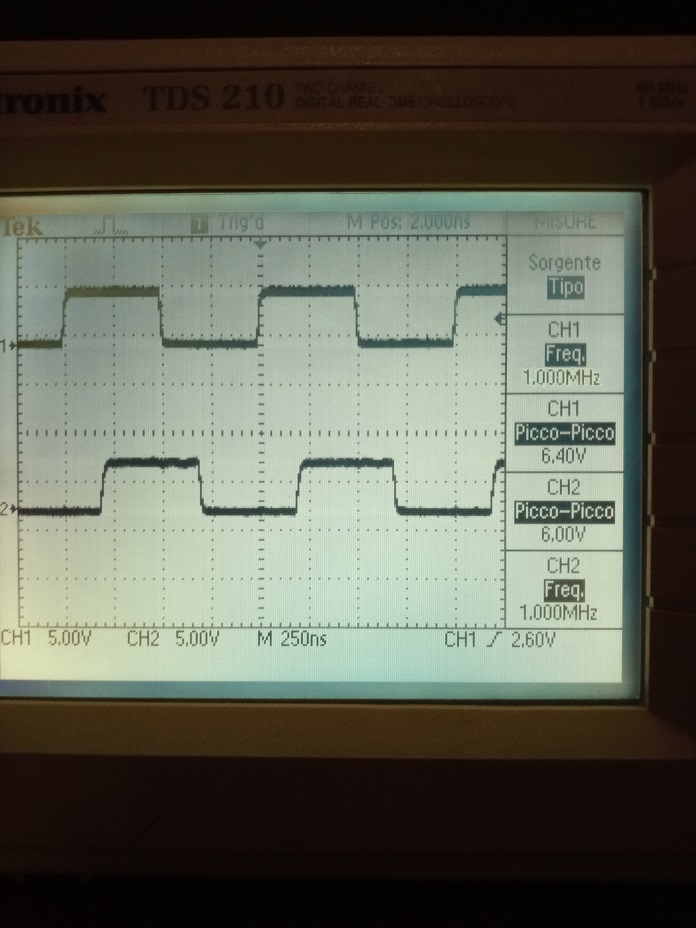

Nella foto successiva è visualizzato:

- Sul canale 1 sempre il segnale di riferimento.

- Sul canale 2 il segnale presente sul diodo D2.

Si noti la frequenza a 2 MHz (66 MHz / 33). Il segnale prelevato sul collettore di T3 è inviato all'ingresso clock del flip-flop IC2 che divide per due la frequenza in ingresso, nella foto successiva è visualizzato:

- Sul canale 1 sempre il segnale di riferimento.

- Sul canale 2 il segnale presente sul pin 2 e 5 di IC2.

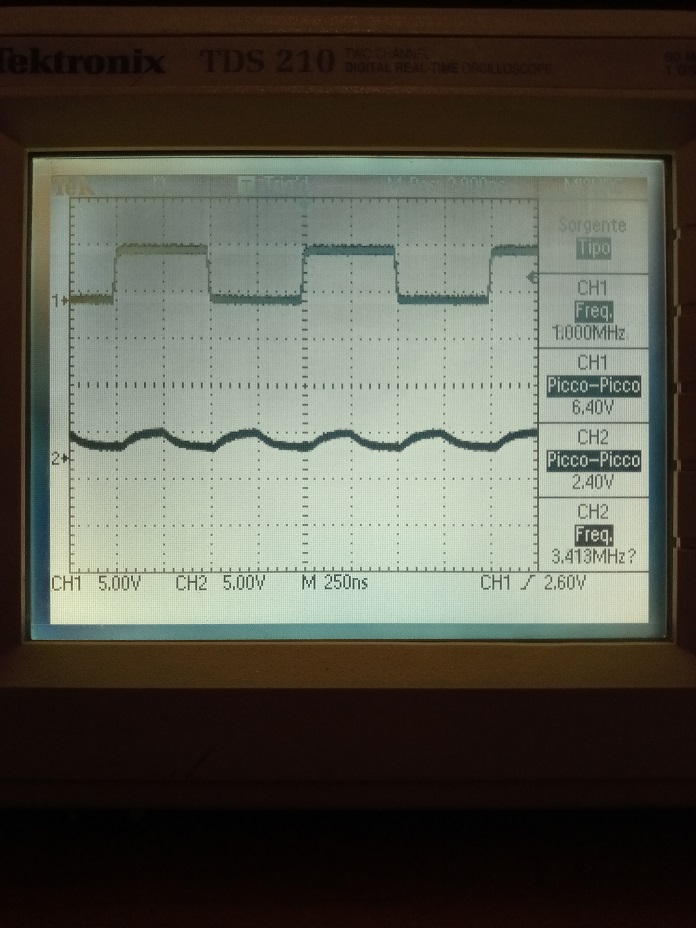

Si noti che ora i segnali hanno la stessa frequenza ma sono sfasati di circa 90°, condizione di aggancio per un valore di tensione continua ai capi del diodo varicap di circa 2.5V. Nella foto successiva viene visualizzato:

- Sul canale 1 sempre il segnale di riferimento.

- Sul canale 2 il segnale presente ai capi di C6.

Il valore della tensione continua ai capi di C6 è 2.25V.

Il circuito è semplice ma mantiene la frequenza a 66 MHz rigorosamente costante. Per poter verificare questa costanza ho tenuto in funzione il PLL per diverse ore monitorandolo con un ricevitore FM.

Ciao.

Fabio