INTRODUZIONE

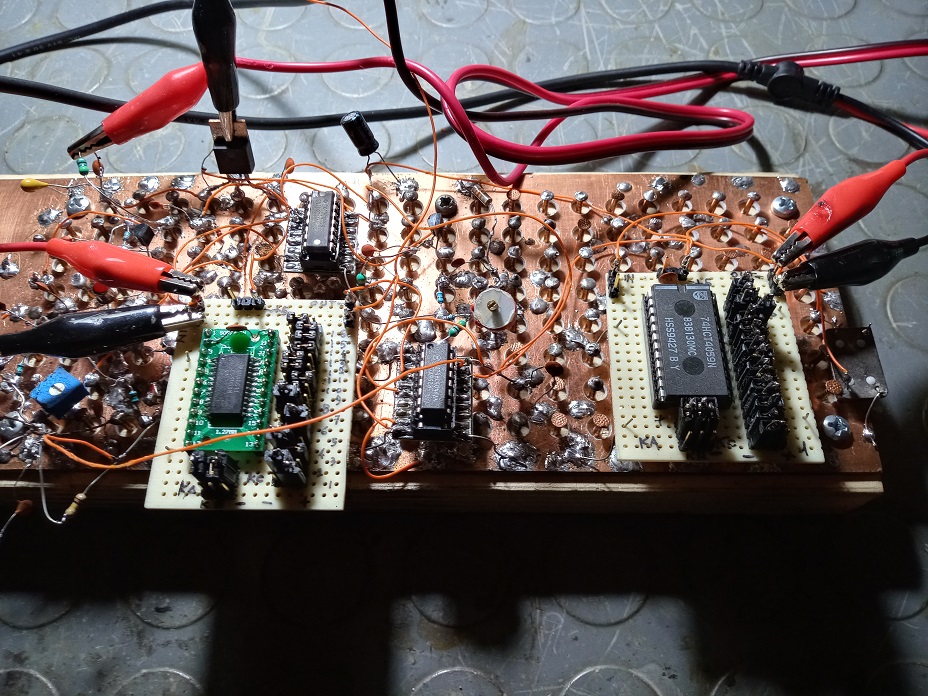

Quello che propongo in questa pagina è un sintetizzatore di frequenze CB a PLL; il relativo circuito genera, con un segnale di riferimento ad 1MHz, tutte le frequenze CB dal canale 1 al canale 40 distanziate tra di loro di 10 KHz .

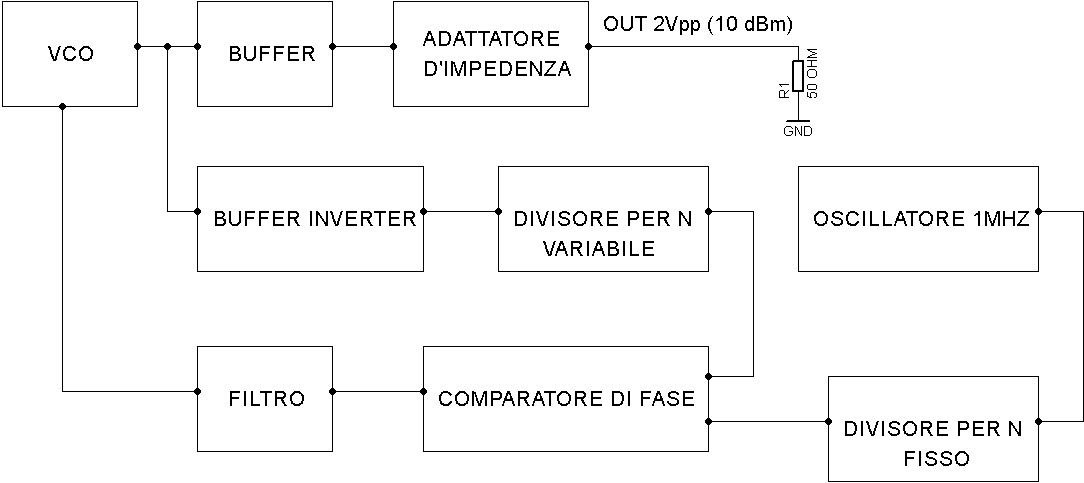

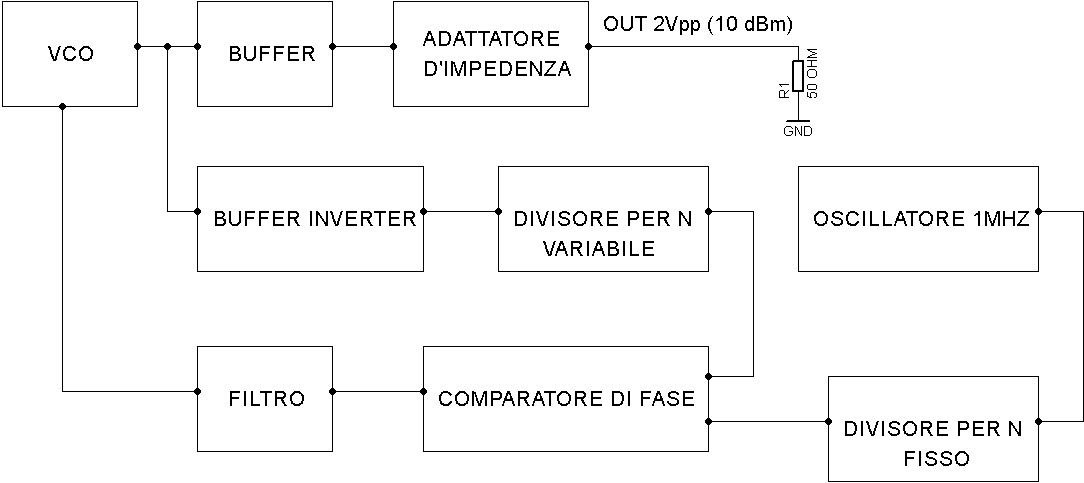

Qui sotto lo schema a blocchi:

Facendo un esempio immaginiamo che il PLL sia agganciato e la frequenza di uscita sia 27.185 MHz (canale 19) corrispondente al centro banda CB. In queste condizioni la tensione errore all'uscita del comparatore di fase, tramite il filtro, fa si che ai capi dei due diodi varicap ci siano circa 2.5V (come è stato scelto per questo progetto), la tensione errore si può ritenere costante (a parte le piccole ondulazioni che esistono sempre in tutti i sistemi a catena chiusa e servono per attuare piccole correzioni rispetto ai valori centrali) ed è per questo che viene definita statica.

In questa situazione, come ho già scritto, le due frequenze all'ingresso del comparatore sono uguali e pari a 5 KHz. Una è quella riferimento ricavata dall'oscillatore da 1MHz divisa per 200 (tramite il DIVISORE FISSO), l'altra è quella derivata dalla frequenza generata dal VCO divisa, (tramite il DIVISORE VARIABILE), per 5437 (divisore N) in questo caso infatti:

27185000 / 5000 = 5437

Non confondere le quantità statiche con quelle dinamiche, queste ultime intervengono solo quando c'è un brusco cambio di frequenza e si estinguono dopo un certo periodo di tempo quando il sistema è tornato a funzionare a regime (ovvero quando la nuova frequenza sintonizzata è divenuta stabile).

Infatti se si effettua un cambio del divisore N il PLL si trova d'un tratto a gestire un improvviso salto di frequenza e cerca di ripristinare la eguaglianza tra le due frequenze a 5000 Hz, la reazione non è istantanea perché la catena chiusa VCO-DIVISORE-COMPARATORE-FILTRO-VCO costituisce un filtro di secondo ordine e come tutti i filtri esso non risponde in modo istantaneo a improvvisi cambi di quantità che prima erano statiche.

Qui entra in ballo la tensione errore dinamica; ci sarà una forte variazione di quest'ultima per l'improvviso cambio di fase tra i due segnali all'ingresso del comparatore, dopo un certo periodo di tempo (vedremo poi come si calcola questo periodo di tempo) la nuova frequenza sintonizzata si stabilizzerà con un nuovo angolo di fase statico e una nuova tensione continua ai capi dei diodi varicap (con i varicap minore è la tensione ai loro capi più alta è la capacità che presentano ai loro terminali e quindi più è bassa la frequenza di oscillazione del VCO). Dopo questo periodo di tempo tutti i segnali dinamici si estinguono e le due frequenze agli ingressi del comparatore di fase tornano ad essere uguali ma sfasati in quantità diversa di come lo erano alla frequenza di 27.185 MHz appunto per generare la nuova tensione continua.

Lo schema è il seguente:

Il VCO riesce ad oscillare tra 23 MHz a 29.7 MHz (a catena aperta) con le seguenti tensioni applicate ai diodi varicap (DRV5610):

VC = 0V il VCO oscilla a 23 MHz

VC = 5V il VCO oscilla a 29.7 MHz

Per la banda CB che interessa a noi (a catena chiusa):

26.965 MHz VC = 2.357V (canale 1)

27.185 MHz VC = 2.5V (centro banda, canale 19)

27.405 MHz VC = 2.642V (canale 40)

La scelta di utilizzare due diodi in connessione "back-to-back" è stata resa necessaria per abbassare la distorsione del segnale RF generato, infatti usando un solo diodo varicap si va incontro al fenomeno di modulazione di capacità, ovvero il segnale a RF aumentando e diminuendo di livello va a modulare il diodo (e quindi la sua capacità) rispetto alla posizione di riposo. Per una regola empirica si considera trascurabile questa modulazione quando il picco del segnale RF (VRp) è minore del 15% della tensione continua. ovvero quando:

VRp < 15% VCmin = 2.5V < 0.36V

il che, come si vede, in questo circuito non è confermato.

Utilizzando due diodi in connessione "back-to-back" il fenomeno della modulazione si attenua di molto, infatti quando è presente un segnale RF ai capi della serie dei varicap, per un semiperiodo la tensione inversa su un diodo aumenta mentre quella presente sull'altro diodo diminuisce, per l'altro semiperiodo si invertono i ruoli dei diodi, in questo modo le variazioni di capacità su ogni varicap avvengono in senso opposto mantenendo la capacità della serie costante.

Ho fatto delle prove sul circuito prima usando un solo varicap e poi usandone due; il risultato è evidente, nel primo caso l'oscillatore generava un segnale molto distorto (semionda positiva a punta e quella negativa schiacciata), nel secondo caso, invece, il segnale è quasi sinusoidale.

La resistenza R9 da 1M serve per isolare il gruppo risonante dal filtro che alimenta i diodi varicap.

La resistenza di uscita del VCO è piuttosto alta e quindi quest'ultimo non è in grado di pilotare direttamente un carico di 50 ohm. Per questo motivo è stato inserito tra l'uscita del VCO ed il carico un buffer a JFET (2N3819) ed un adattatore passivo per adattare l'impedenza di uscita del JFED al carico di 50 ohm.

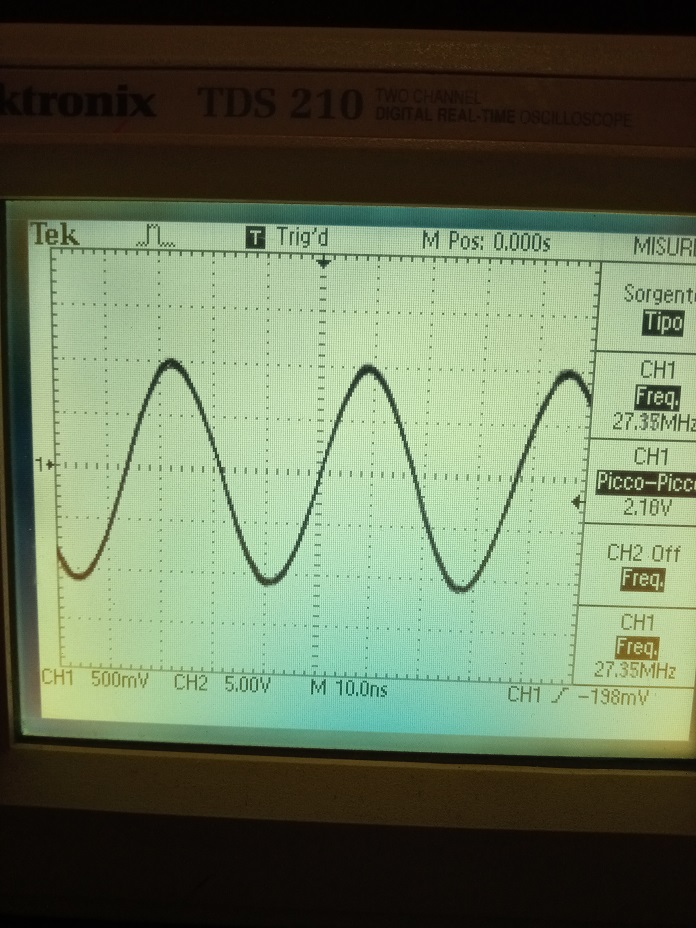

L'impedenza di uscita del JFET è 150 + j20 ohm e dato che il segnale generato dal VCO è quasi di forma sinusoidale non occorre un adattatore d'impedenza altamente selettivo, quello che ho usato infatti ha una banda quasi piatta per tutte le frequenze CB. I dati sono i seguenti:

Massimo livello disponibile = 2Vpp pari a 10dBm.

Banda passante @ -1 dB = 26.965 MHz - 27.405 MHz

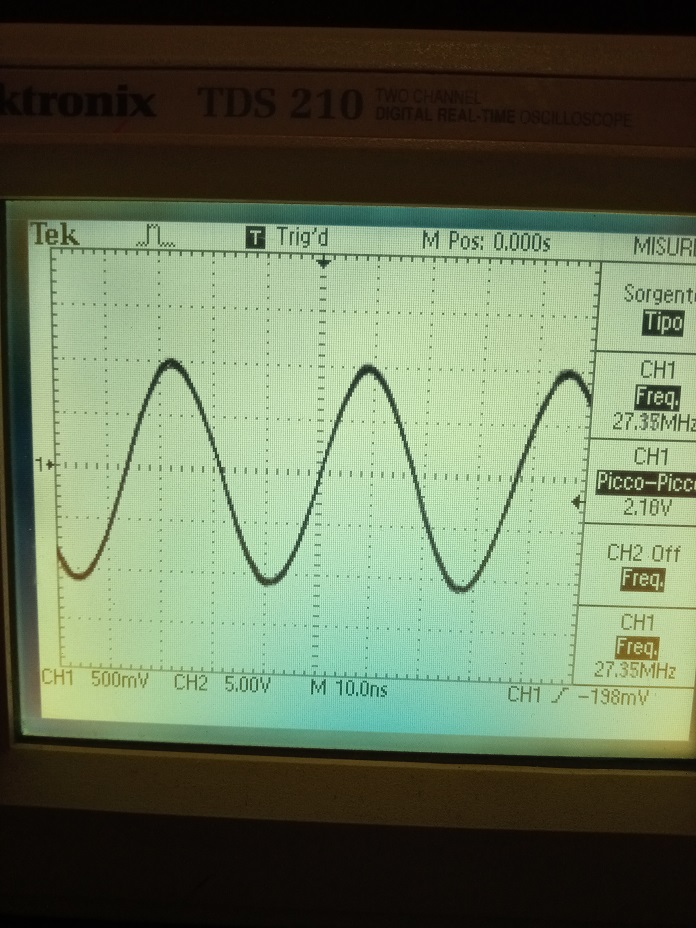

In foto la forma d'onda sul carico e la frequenza:

Qui sotto lo schema a blocchi:

PANORAMICA SUL FUNZIONAMENTO DEL SISTEMA

Quando

il PLL è agganciato i segnali presenti all'ingresso del

comparatore sono alla stessa frequenza (sempre 5KHz per ogni frequenza

CB) ma sfasati tra di loro di un angolo (statico) che dipende

dalla frequenza CB sintonizzata. Questo sfasamento produce all'uscita del comparatore un segnale errore (statico)

che tramite il filtro fornisce una tensione continua al VCO facendolo

oscillare sulla frequenza prescelta. Facendo un esempio immaginiamo che il PLL sia agganciato e la frequenza di uscita sia 27.185 MHz (canale 19) corrispondente al centro banda CB. In queste condizioni la tensione errore all'uscita del comparatore di fase, tramite il filtro, fa si che ai capi dei due diodi varicap ci siano circa 2.5V (come è stato scelto per questo progetto), la tensione errore si può ritenere costante (a parte le piccole ondulazioni che esistono sempre in tutti i sistemi a catena chiusa e servono per attuare piccole correzioni rispetto ai valori centrali) ed è per questo che viene definita statica.

In questa situazione, come ho già scritto, le due frequenze all'ingresso del comparatore sono uguali e pari a 5 KHz. Una è quella riferimento ricavata dall'oscillatore da 1MHz divisa per 200 (tramite il DIVISORE FISSO), l'altra è quella derivata dalla frequenza generata dal VCO divisa, (tramite il DIVISORE VARIABILE), per 5437 (divisore N) in questo caso infatti:

27185000 / 5000 = 5437

Non confondere le quantità statiche con quelle dinamiche, queste ultime intervengono solo quando c'è un brusco cambio di frequenza e si estinguono dopo un certo periodo di tempo quando il sistema è tornato a funzionare a regime (ovvero quando la nuova frequenza sintonizzata è divenuta stabile).

Infatti se si effettua un cambio del divisore N il PLL si trova d'un tratto a gestire un improvviso salto di frequenza e cerca di ripristinare la eguaglianza tra le due frequenze a 5000 Hz, la reazione non è istantanea perché la catena chiusa VCO-DIVISORE-COMPARATORE-FILTRO-VCO costituisce un filtro di secondo ordine e come tutti i filtri esso non risponde in modo istantaneo a improvvisi cambi di quantità che prima erano statiche.

Qui entra in ballo la tensione errore dinamica; ci sarà una forte variazione di quest'ultima per l'improvviso cambio di fase tra i due segnali all'ingresso del comparatore, dopo un certo periodo di tempo (vedremo poi come si calcola questo periodo di tempo) la nuova frequenza sintonizzata si stabilizzerà con un nuovo angolo di fase statico e una nuova tensione continua ai capi dei diodi varicap (con i varicap minore è la tensione ai loro capi più alta è la capacità che presentano ai loro terminali e quindi più è bassa la frequenza di oscillazione del VCO). Dopo questo periodo di tempo tutti i segnali dinamici si estinguono e le due frequenze agli ingressi del comparatore di fase tornano ad essere uguali ma sfasati in quantità diversa di come lo erano alla frequenza di 27.185 MHz appunto per generare la nuova tensione continua.

Lo schema è il seguente:

VCO

Il VCO è costituito da un oscillatore Colpitts con

controllo di guadagno automatico. Il segnale viene prelevato, tramite

C3, dal collettore di T1 (2N3904) e riportato al suo emettitore

attraverso il JFET Q1 (2N3819). In questo modo si realizza una

retroazione positiva. Q1 serve per non caricare il gruppo risonante

composto dai due varicap, il condensatore variabile C16 e

dall'induttanza L5. Q2 è un JFET (VCR4N) ottimizzato dal costruttore

per funzionare come dispositivo a resistenza variabile, a zero volt

applicati tra gate e source esso presenta il valore di resistenza

più basso tra drain e source, questa resistenza aumenta per valori di

tensioni negativi e raggiunge valori piuttosto alti vicino

all'interdizione. Questo JFET serve a tenere costante il livello del

segnale al variare della frequenza di oscillazione, il funzionamento è

il seguente; mediante il diodo D1 ed il condensatore C6 si raddrizza e

si livella rispettivamente il segnale prelevato dal collettore di T1,

quindi ai capi di R5 è presente una tensione negativa all'incirca

proporzionale al picco del segnale RF generato, maggiore è il livello

di quest'ultimo e maggiore è il livello della tensione continua

negativa. All'accensione non si è ancora innescata l'oscillazione e

tra il gate ed il source di Q2 la tensione è a zero volt, quindi il

JFET presenta tra il drain ed il source una bassa resistenza. In queste

condizioni il guadagno complessivo dell'oscillatore è al suo massimo

valore e l'oscillazione può instaurarsi rapidamente, allora il segnale

RF aumenta di livello e aumenta corrispondentemente la tensione continua

negativa che fa abbassare la resistenza di Q2 riducendo il guadagno del VCO. A

equilibrio raggiunto il livello sul collettore di T1, in tutta la banda CB, è pari a 5 Vpp con

una variazione tra i 26.965 MHz (canale 1) ed i 27.405 MHz (canale 40)

di solo 0.5 dB.Il VCO riesce ad oscillare tra 23 MHz a 29.7 MHz (a catena aperta) con le seguenti tensioni applicate ai diodi varicap (DRV5610):

VC = 0V il VCO oscilla a 23 MHz

VC = 5V il VCO oscilla a 29.7 MHz

Per la banda CB che interessa a noi (a catena chiusa):

26.965 MHz VC = 2.357V (canale 1)

27.185 MHz VC = 2.5V (centro banda, canale 19)

27.405 MHz VC = 2.642V (canale 40)

La scelta di utilizzare due diodi in connessione "back-to-back" è stata resa necessaria per abbassare la distorsione del segnale RF generato, infatti usando un solo diodo varicap si va incontro al fenomeno di modulazione di capacità, ovvero il segnale a RF aumentando e diminuendo di livello va a modulare il diodo (e quindi la sua capacità) rispetto alla posizione di riposo. Per una regola empirica si considera trascurabile questa modulazione quando il picco del segnale RF (VRp) è minore del 15% della tensione continua. ovvero quando:

VRp < 15% VCmin = 2.5V < 0.36V

il che, come si vede, in questo circuito non è confermato.

Utilizzando due diodi in connessione "back-to-back" il fenomeno della modulazione si attenua di molto, infatti quando è presente un segnale RF ai capi della serie dei varicap, per un semiperiodo la tensione inversa su un diodo aumenta mentre quella presente sull'altro diodo diminuisce, per l'altro semiperiodo si invertono i ruoli dei diodi, in questo modo le variazioni di capacità su ogni varicap avvengono in senso opposto mantenendo la capacità della serie costante.

Ho fatto delle prove sul circuito prima usando un solo varicap e poi usandone due; il risultato è evidente, nel primo caso l'oscillatore generava un segnale molto distorto (semionda positiva a punta e quella negativa schiacciata), nel secondo caso, invece, il segnale è quasi sinusoidale.

La resistenza R9 da 1M serve per isolare il gruppo risonante dal filtro che alimenta i diodi varicap.

BUFFER E ADATTATORE D'IMPEDENZA

La resistenza di uscita del VCO è piuttosto alta e quindi quest'ultimo non è in grado di pilotare direttamente un carico di 50 ohm. Per questo motivo è stato inserito tra l'uscita del VCO ed il carico un buffer a JFET (2N3819) ed un adattatore passivo per adattare l'impedenza di uscita del JFED al carico di 50 ohm.

L'impedenza di uscita del JFET è 150 + j20 ohm e dato che il segnale generato dal VCO è quasi di forma sinusoidale non occorre un adattatore d'impedenza altamente selettivo, quello che ho usato infatti ha una banda quasi piatta per tutte le frequenze CB. I dati sono i seguenti:

Massimo livello disponibile = 2Vpp pari a 10dBm.

Banda passante @ -1 dB = 26.965 MHz - 27.405 MHz

In foto la forma d'onda sul carico e la frequenza:

INVERTER

Anche

se il DIVISORE VARIABILE può accettare segnali di qualsiasi

forma purché periodici, per renderlo immune dal livello degli stessi

occorre inserire tra il VCO ed il DIVISORE un trigger di

schmitt. Ovviamente dato che la frequenza del segnale è abbastanza alta

occorre usarne uno del tipo veloce e il CD74HC14 fa al caso

nostro. Il condensatore C7 e il diodo D2 hanno il compito di "clempare"

il segnale sinusoidale; avendo quest'ultimo un livello di 5 Vpp,

in uscita del clamp si ha un segnale con un picco positivo di +4.7 V ed

uno negativo di -0.7 V. Per una regola empirica il clamper funziona bene

affinché è soddisfatta la seguente relazione:

RL * C > 100*T

dove RL è la resistenza vista all'ingresso dell'integrato e T è il periodo del segnale.

Ho riportato la suddetta formula solo per correttezza progettuale dato che non dobbiamo preoccuparci di fare calcoli per il fatto che la resistenza d'ingresso dell'inverter è talmente elevata che condensatori dell'ordine del nF sono più che sufficienti.

RL * C > 100*T

dove RL è la resistenza vista all'ingresso dell'integrato e T è il periodo del segnale.

Ho riportato la suddetta formula solo per correttezza progettuale dato che non dobbiamo preoccuparci di fare calcoli per il fatto che la resistenza d'ingresso dell'inverter è talmente elevata che condensatori dell'ordine del nF sono più che sufficienti.

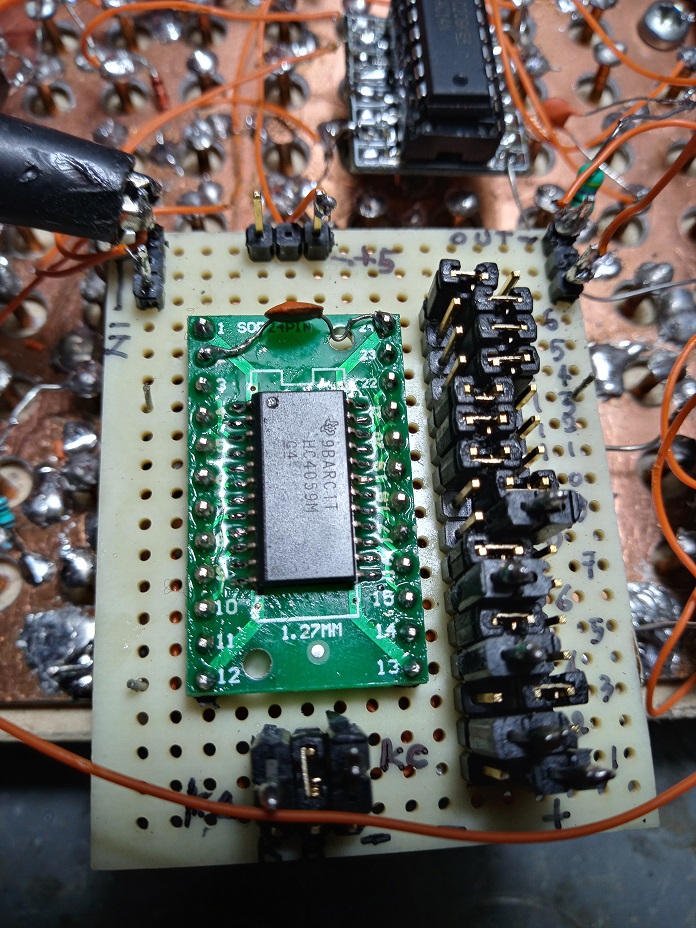

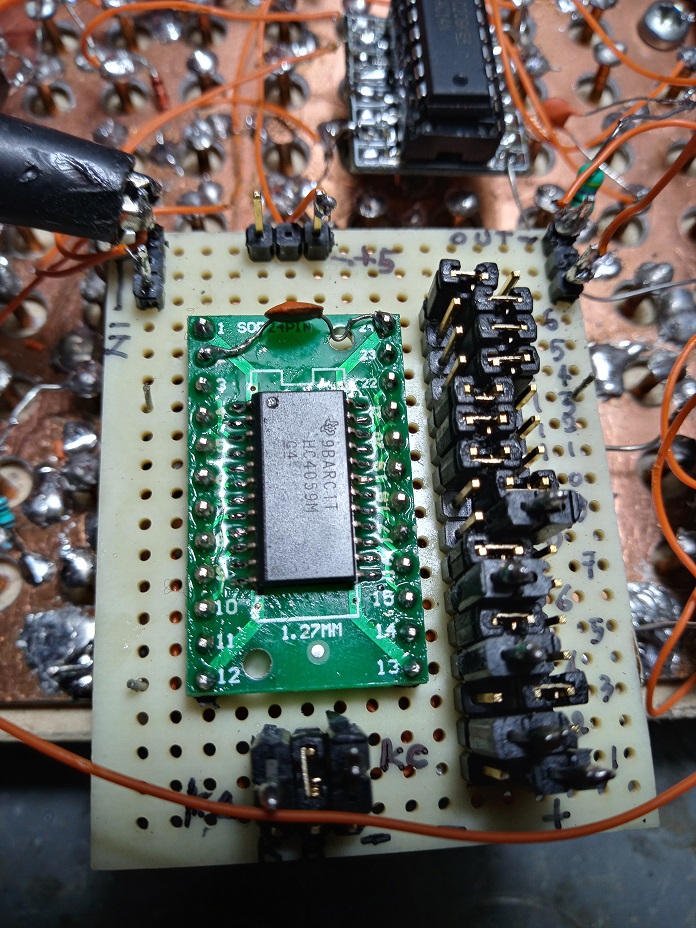

DIVISORE VARIABILE

Questo

integrato (CD74HC4059) è un divisore di frequenza programmabile che

permettere di dividere da 3 a 15999 (N) la frequenza del segnale in

ingresso, esso fornisce in uscita impulsi larghi un periodo del segnale

d'ingresso con frequenza pari a quella d'ingresso divisa N.

La formula su cui si basa il calcolo di N è la seguente:

N = MODE * (preset valore) + resto = MODE * (migliaia + centinaia + decine + unità) + resto

ed in particolare::

N = MODE * ( D5 * 1000 + D4 * 100 + D3 * 10 + D2 * 1) + D1

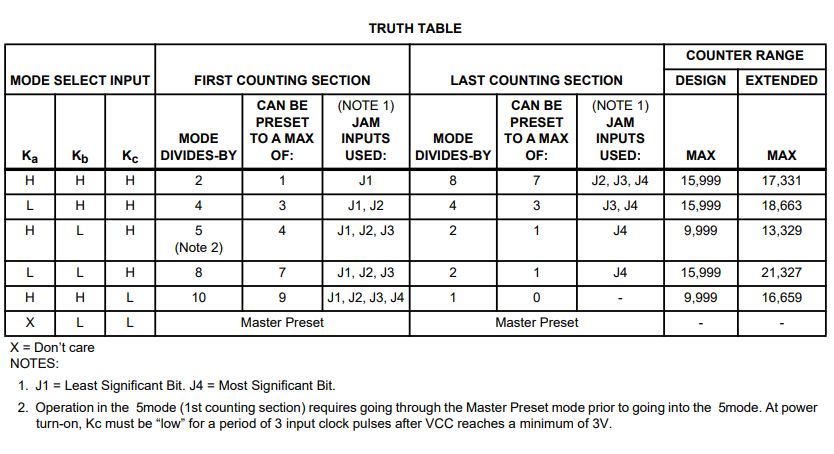

Le due tabelle seguenti servono per il calcolo:

Ma partiamo subito con un esempio. Ammettiamo che desideriamo che il PLL si agganci sulla frequenza 26.965 MHz, siccome bisogna ottenere sempre una frequenza di 5000 HZ all'uscita del DIVISORE VARIABILE, ricaviamo N (divisore):

N = 26965000 / 5000 = 5393

in base a questo valore, tramite la colonna DESIGN sotto COUNTER RANGE scegliamo il mode, il valore calcolato di N deve essere inferiore o uguale al massimo riportato in questa colonna. In questo caso possiamo scegliere tutti i MODE (evitare, se possibile, sempre il MODE 5 perché ci sono complicazioni circuitali con esso), decido per il MODE 2.

Nella colonna JAMP INPUT USED sotto FIRST COUNTING SECTION con il MODE 2 abbiamo a disposizione per il resto (D1) solo J1, mentre nella colonna JAMP INPUT USED sotto LAST COUNTING SECTION abbiamo a disposizione J2, J3, J4 (D5) per le migliaia del preset, gli altri gruppi di quattro bit hanno i seguenti significati:

D2 = unità del preset (J8 J7 J6 J5)

D3 = decine del preset (J12 J11 J10 J9)

D4 = centinaia del preset (J16 J15 J14 J13)

Ricavo il preset valore:

preset valore = N / MODE = 5393 / 2 = 2696 con il resto di 1 (il resto lo si può calcolare anche con la calcolatrice di Windows, con il tasto "mod").

imposto quindi il resto a 1:

D1 = J1 = 1

imposto le migliaia, le centinaia, le decine e le unità del preset:

D5 = J4 J3 J2 = 2 = 010b (migliaia)

D4 = J16 J15 J14 J13 = 6 = 0110b (centinaia)

D3 = 9 = J12 J11 J10 J9 = 9 = 1001b (decine)

D2 = 6 = J8 J7 J6 J5 = 6 = 0110B (unità)

ricapitolando la programmazione dei JAM (16 bit) è la seguente.

J16...J1 = 0110100101100101b

come conferma:

N = MODE * ( D5 * 1000 + D4 * 100 + D3 * 10 + D2 * 1) + D1 = 2 * 2696 + 1 = 5963

i conti tornano.

Ho usato per impostare i JAM a "0" o a "1" dei ponticelli, certo, è un po' scomodo, comunque in questa pagina c'è la possibilità di programmare il CD4059 con Arduino.

Qui di seguito riporto una tabella con i canali, le frequenze CB, il valore di N ed i valori binari dei JAM calcolati (con molta pazienza).

Come si nota essendo la distanza tra due frequenze consecutive sempre 10KHz occorre incrementare (o decrementare) N di due unità per passare da una all'altra (2 * 5000 = 10KHz).

La formula su cui si basa il calcolo di N è la seguente:

N = MODE * (preset valore) + resto = MODE * (migliaia + centinaia + decine + unità) + resto

ed in particolare::

N = MODE * ( D5 * 1000 + D4 * 100 + D3 * 10 + D2 * 1) + D1

Le due tabelle seguenti servono per il calcolo:

Ma partiamo subito con un esempio. Ammettiamo che desideriamo che il PLL si agganci sulla frequenza 26.965 MHz, siccome bisogna ottenere sempre una frequenza di 5000 HZ all'uscita del DIVISORE VARIABILE, ricaviamo N (divisore):

N = 26965000 / 5000 = 5393

in base a questo valore, tramite la colonna DESIGN sotto COUNTER RANGE scegliamo il mode, il valore calcolato di N deve essere inferiore o uguale al massimo riportato in questa colonna. In questo caso possiamo scegliere tutti i MODE (evitare, se possibile, sempre il MODE 5 perché ci sono complicazioni circuitali con esso), decido per il MODE 2.

Nella colonna JAMP INPUT USED sotto FIRST COUNTING SECTION con il MODE 2 abbiamo a disposizione per il resto (D1) solo J1, mentre nella colonna JAMP INPUT USED sotto LAST COUNTING SECTION abbiamo a disposizione J2, J3, J4 (D5) per le migliaia del preset, gli altri gruppi di quattro bit hanno i seguenti significati:

D2 = unità del preset (J8 J7 J6 J5)

D3 = decine del preset (J12 J11 J10 J9)

D4 = centinaia del preset (J16 J15 J14 J13)

Ricavo il preset valore:

preset valore = N / MODE = 5393 / 2 = 2696 con il resto di 1 (il resto lo si può calcolare anche con la calcolatrice di Windows, con il tasto "mod").

imposto quindi il resto a 1:

D1 = J1 = 1

imposto le migliaia, le centinaia, le decine e le unità del preset:

D5 = J4 J3 J2 = 2 = 010b (migliaia)

D4 = J16 J15 J14 J13 = 6 = 0110b (centinaia)

D3 = 9 = J12 J11 J10 J9 = 9 = 1001b (decine)

D2 = 6 = J8 J7 J6 J5 = 6 = 0110B (unità)

ricapitolando la programmazione dei JAM (16 bit) è la seguente.

J16...J1 = 0110100101100101b

come conferma:

N = MODE * ( D5 * 1000 + D4 * 100 + D3 * 10 + D2 * 1) + D1 = 2 * 2696 + 1 = 5963

i conti tornano.

Ho usato per impostare i JAM a "0" o a "1" dei ponticelli, certo, è un po' scomodo, comunque in questa pagina c'è la possibilità di programmare il CD4059 con Arduino.

Qui di seguito riporto una tabella con i canali, le frequenze CB, il valore di N ed i valori binari dei JAM calcolati (con molta pazienza).

| CANALE | FREQUENZA MHz | N | J16 | J15 | J14 | J13 | J12 | J11 | J10 | J9 | J8 | J7 | J6 | J5 | J4 | J3 | J2 | J1 |

| 1 | 26.965 | 5393 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 2 | 26.975 | 5395 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 3 | 26.985 | 5397 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 4 | 27.005 | 5401 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 5 | 27.015 | 5403 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 6 | 27.025 | 5405 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 7 | 27.035 | 5407 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 8 | 27.055 | 5411 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 9 | 27.065 | 5413 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 10 | 27.075 | 5415 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 11 | 27.085 | 5417 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 12 | 27.105 | 5421 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 13 | 27.115 | 5423 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 14 | 27.125 | 5425 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 15 | 27.135 | 5427 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 16 | 27.155 | 5431 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 17 | 27.165 | 5433 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 18 | 27.175 | 5435 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 19 | 27.185 | 5437 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 20 | 27.205 | 5441 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 21 | 27.215 | 5443 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 22 | 27.225 | 5445 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 23 | 27.255 | 5451 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 24 | 27.235 | 5447 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 25 | 27.245 | 5449 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 26 | 27.265 | 5453 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 27 | 27.275 | 5455 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 28 | 27.285 | 5457 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 29 | 27.295 | 5459 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 30 | 27.305 | 5461 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 31 | 27.315 | 5463 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 32 | 27.325 | 5465 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 33 | 27.335 | 5467 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| 34 | 27.345 | 5469 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 35 | 27.355 | 5471 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 36 | 27.365 | 5473 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 37 | 27.375 | 5475 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 38 | 27.385 | 5477 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 39 | 27.395 | 5479 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 40 | 27.405 | 5481 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

Come si nota essendo la distanza tra due frequenze consecutive sempre 10KHz occorre incrementare (o decrementare) N di due unità per passare da una all'altra (2 * 5000 = 10KHz).

DIVISORE FISSO

Il

compito di questo DIVISORE FISSO è quello di dividere la

frequenza di riferimento dell'oscillatore quarzato a 1MHz per portarla

a 5KHz, quindi N è:

N = 1000000/5000 = 200

Con il metodo descritto per il DIVISORE VARIABILE si calcolano facilmente i livelli logici necessari per i JAM affinché il chip divida per 200. Dato che N è fisso si possono tranquillamente saldare i pin dei JAM a +5 o a GND.

Per questo divisore si può anche usare il CD4059 il quale è in grado di gestire tranquillamente frequenze di 1 MHz.

N = 1000000/5000 = 200

Con il metodo descritto per il DIVISORE VARIABILE si calcolano facilmente i livelli logici necessari per i JAM affinché il chip divida per 200. Dato che N è fisso si possono tranquillamente saldare i pin dei JAM a +5 o a GND.

Per questo divisore si può anche usare il CD4059 il quale è in grado di gestire tranquillamente frequenze di 1 MHz.

COMPARATORE DI FASE

Come

già evidenziato sopra i due divisori forniscono alle loro uscite

un impulso e non una onda quadra con duty-cicle al 50 % , per questo

non è possibile usare un COMPARATORE DI FASE a xor che lavora

sui livelli. Ci sono però altri due tipi di comparatori di fase

abbastanza conosciuti, il primo è il comparatore di fase a

flip-flop, il secondo è il comparatore di fase PFD, io ho deciso di

usare il secondo dato che è sensibile sia alla fase che alla frequenza.

Ho usato l'integrato 74HC4046 (va bene anche il CD4046 date le basse frequenze in gioco) che contiene tre comparatori di fase e tra essi c'è anche il PDF che serve a noi.

Qui di seguito la procedura per il dimensionamento del filtro.

Si calcola il guadagno del comparatore PFD:

Kd = VDD / (4 * Pi) = 5 / (4 * Pi) = 0.39 V/rad

Si calcola il guadagno del VCO:

Ko = (2 * Pi * (frequenza massima - frequenza minima)) / (tensione massima - tensione minima) = (2 * Pi * (27405000 - 26965000)) / (2.642 - 2.357) = 9666439 rad/sec/V

Si calcola in numero di N minimo (Nm) e il numero di N massimo (NM), dalla tabella in alto:

Nm = 5393

NM = 5481

Si sceglie il damping factor pari a 0.7 (Df) che da una risposta piatta, si controlla se il minimo ed il massimo del damping factor (variabile con N) rimanga dentro i limiti 0.5 e 1 (valori ottimali):

Nmean = sqrt(Nm * NM) = sqrt(5393 * 5481) = 5436.8

Dfm = Df * sqrt(Nm / Nmean) = 0.7 * sqrt(5393 / 5436.8) = 0.69

DfM= Df * sqrt(NM / Nmean) = 0.7 * sqrt(5481 / 5436.8) = 0.702

Sia il minimo che il massimo rimangono dentro i valori ottimali, si può quindi procedere con il dimensionamento. Si sceglie ora il tempo necessario per l'aggancio (TL) quando si cambia frequenza, un tempo di 20mS è molto breve e va bene. Da questo ricavo la pulsazione naturale wn:

wn = 2 * Pi / TL = 2 * Pi / 0.020 = 314 rad/s

Dalla pulsazione naturale ricavo la somma delle costanti di tempo del filtro:

(t1 + t2) = Ko * Kd / Nmean * wn^2 = 0.39 * 9666439 / 5436.8 * 314^2 = 7 mS

ricavo la costante di tempo t2:

t2 = Df * 2 / wn = 0.7 * 2 / 314 = 4.4 mS

ricavo t1:

t1 = (t1 + t2 ) - t2 = 0.007 - 0.0044 = 2.5 mS

Ricavo le resistenze del filtro imponendo la capacità C14 a 1 uF (è bene scegliere capacità grandi per sopprimere in modo efficace l'effetto sideband):

R10 = t1 / C14 = 2.5 mS / 1 uF = 2K5 => 2K7

R11 = t2 / C14 = 4.4 mS / 1 uF = 4K4 => 4K7

In queste condizioni la banda di frequenza (metà) in lock-range è:

fl = 2 * Df * wn = 2 * 0.7 * 314 = 439 Hz

La condizione peggiore per il PLL è quando si passa dal canale 40 al canale 1 (o viceversa), infatti se ad esempio il PLL è agganciato sui 27405000 Hz (con N = 5481) e si commuta N a 5393 (corrispondente al canale 1) per un istante la frequenza all'ingresso del comparatore passa da 5000 a 5081.5 (27405000 / 5393 = 5081.5) con una variazione delta _f = 5081.5 - 5000 = 81.5 Hz. Questo salto di frequenza è ben più piccolo della frequenza del lock-range, il sistema reagirà quindi nel tempo TL.

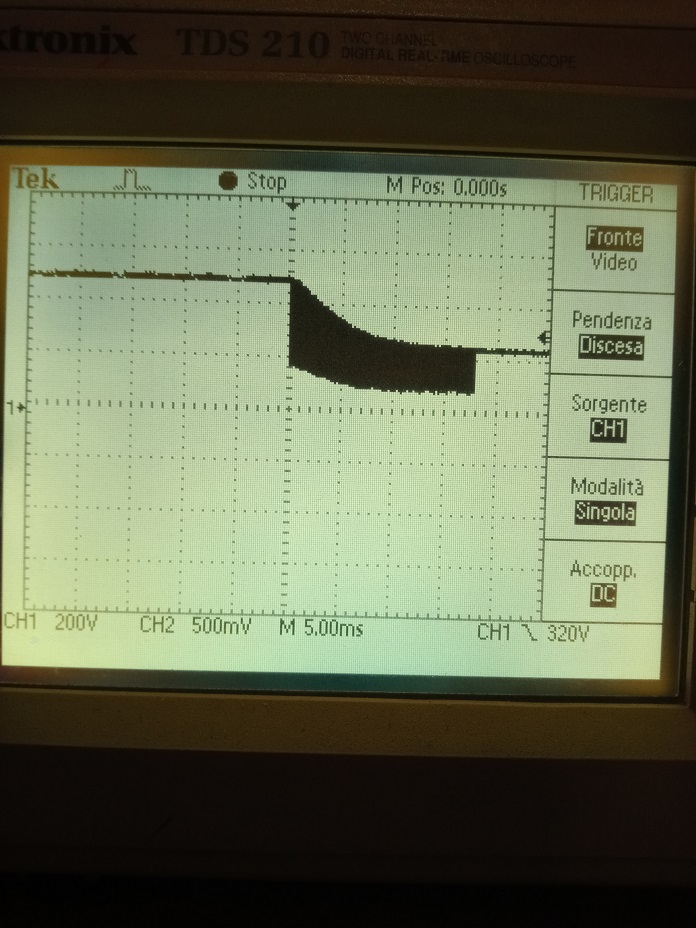

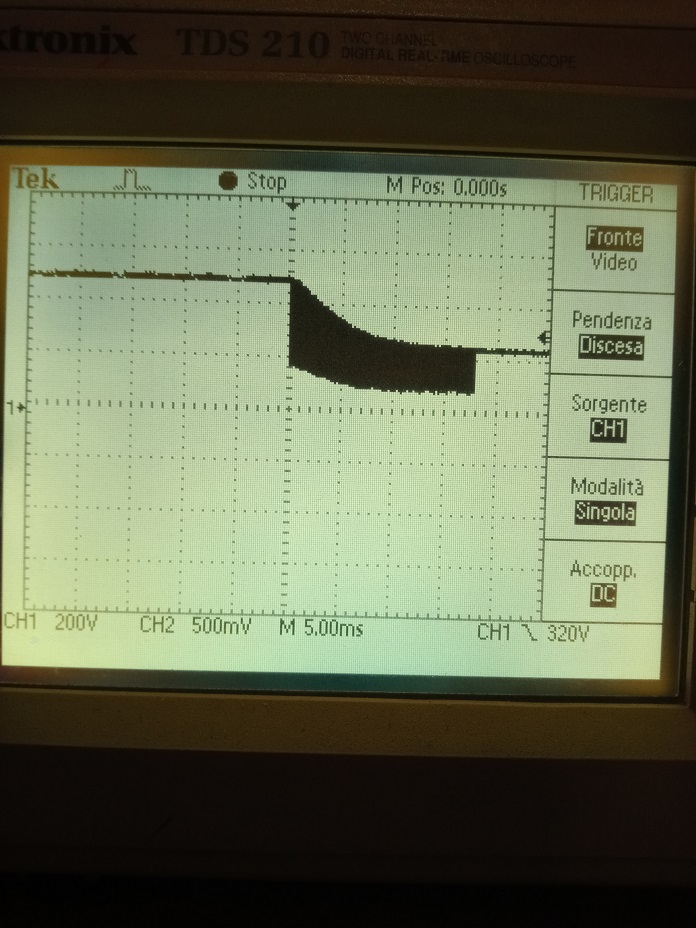

Qui sotto una istantanea della tensione continua errore per un passaggio (esagerato per questo progetto) da 27405000 Hz a 29000000 Hz, in questo caso il salto è da 5000 Hz a 5291 Hz (29000000 / 5481 = 5291) con una delta_ f = 5291 - 5000 = 291 Hz che rientra sempre nella frequenza del lock-range infatti, come si nota dalla immagine, il tempo richiesto d PLL per portare la tensione corrispondente ai 29 MHz a quella corrispondente ai 27.405 MHz ci mette circa il tempo (TL) deciso a priori.

Ho usato l'integrato 74HC4046 (va bene anche il CD4046 date le basse frequenze in gioco) che contiene tre comparatori di fase e tra essi c'è anche il PDF che serve a noi.

Qui di seguito la procedura per il dimensionamento del filtro.

Si calcola il guadagno del comparatore PFD:

Kd = VDD / (4 * Pi) = 5 / (4 * Pi) = 0.39 V/rad

Si calcola il guadagno del VCO:

Ko = (2 * Pi * (frequenza massima - frequenza minima)) / (tensione massima - tensione minima) = (2 * Pi * (27405000 - 26965000)) / (2.642 - 2.357) = 9666439 rad/sec/V

Si calcola in numero di N minimo (Nm) e il numero di N massimo (NM), dalla tabella in alto:

Nm = 5393

NM = 5481

Si sceglie il damping factor pari a 0.7 (Df) che da una risposta piatta, si controlla se il minimo ed il massimo del damping factor (variabile con N) rimanga dentro i limiti 0.5 e 1 (valori ottimali):

Nmean = sqrt(Nm * NM) = sqrt(5393 * 5481) = 5436.8

Dfm = Df * sqrt(Nm / Nmean) = 0.7 * sqrt(5393 / 5436.8) = 0.69

DfM= Df * sqrt(NM / Nmean) = 0.7 * sqrt(5481 / 5436.8) = 0.702

Sia il minimo che il massimo rimangono dentro i valori ottimali, si può quindi procedere con il dimensionamento. Si sceglie ora il tempo necessario per l'aggancio (TL) quando si cambia frequenza, un tempo di 20mS è molto breve e va bene. Da questo ricavo la pulsazione naturale wn:

wn = 2 * Pi / TL = 2 * Pi / 0.020 = 314 rad/s

Dalla pulsazione naturale ricavo la somma delle costanti di tempo del filtro:

(t1 + t2) = Ko * Kd / Nmean * wn^2 = 0.39 * 9666439 / 5436.8 * 314^2 = 7 mS

ricavo la costante di tempo t2:

t2 = Df * 2 / wn = 0.7 * 2 / 314 = 4.4 mS

ricavo t1:

t1 = (t1 + t2 ) - t2 = 0.007 - 0.0044 = 2.5 mS

Ricavo le resistenze del filtro imponendo la capacità C14 a 1 uF (è bene scegliere capacità grandi per sopprimere in modo efficace l'effetto sideband):

R10 = t1 / C14 = 2.5 mS / 1 uF = 2K5 => 2K7

R11 = t2 / C14 = 4.4 mS / 1 uF = 4K4 => 4K7

In queste condizioni la banda di frequenza (metà) in lock-range è:

fl = 2 * Df * wn = 2 * 0.7 * 314 = 439 Hz

La condizione peggiore per il PLL è quando si passa dal canale 40 al canale 1 (o viceversa), infatti se ad esempio il PLL è agganciato sui 27405000 Hz (con N = 5481) e si commuta N a 5393 (corrispondente al canale 1) per un istante la frequenza all'ingresso del comparatore passa da 5000 a 5081.5 (27405000 / 5393 = 5081.5) con una variazione delta _f = 5081.5 - 5000 = 81.5 Hz. Questo salto di frequenza è ben più piccolo della frequenza del lock-range, il sistema reagirà quindi nel tempo TL.

Qui sotto una istantanea della tensione continua errore per un passaggio (esagerato per questo progetto) da 27405000 Hz a 29000000 Hz, in questo caso il salto è da 5000 Hz a 5291 Hz (29000000 / 5481 = 5291) con una delta_ f = 5291 - 5000 = 291 Hz che rientra sempre nella frequenza del lock-range infatti, come si nota dalla immagine, il tempo richiesto d PLL per portare la tensione corrispondente ai 29 MHz a quella corrispondente ai 27.405 MHz ci mette circa il tempo (TL) deciso a priori.

TARATURA

Predisporre il DIVISORE PROGRAMMABILE per la frequenza a centro banda (27.185 MHz), a PLL agganciato regolare C16 per avere 2.5V

ai capi dei diodi varicap. regolare poi C11 per avere il livello

di segnale RF più alto possibile dai capi del carico a 50 ohm.

NOTA:

Gli integrati IC4 e IC2 (nello schema non sono rappresentati i loro pin dell'alimentazione) vanno alimentati a +5V, il regolatore a +5V non è rappresentato nello schema.

Ciao a tutti.

Fabio

NOTA:

Gli integrati IC4 e IC2 (nello schema non sono rappresentati i loro pin dell'alimentazione) vanno alimentati a +5V, il regolatore a +5V non è rappresentato nello schema.

Ciao a tutti.

Fabio