# Capitolo IV

# Progetto del Test Bench

# 4.1 Programma di test

Il test del modulo SCM, a causa della molteplicità dei sistemi in esso contenuti (come si è avuto modo di dedurre dalle argomentazioni precedenti) è decisamente impegnativo. Tuttavia, la complessità attiene all'apparato nella sua interezza, pertanto la Collaborazione ha deciso di effettuare il test di tutti i sistemi attraverso l'utilizzo di banchi di prova (test benches). Tale complessità ricondotta alla costruzione di un sofisticato ed efficace test bench ridurrebbe la fase di test a semplici verifiche esecutive e ripetitive. Nucleo di tutto il test è dunque il test bench, pertanto il suo criterio di progettazione deve necessariamente rispecchiare i criteri di progettazione dell'intero apparato. Sarebbe infatti inutile utilizzare il banco di prova più accurato possibile, senza tenere conto dei criteri di costruzione del modulo oggetto di test e delle sue caratteristiche.

È bene sottolineare che esistono dei sistemi di test commerciali. Questi sono generalmente costruiti in modo modulare per permettere di verificare il funzionamento di apparati di grandi dimensioni, eventualmente anche in condizioni operative. Ciò comporta la necessità di implementare le opportune risorse di test quali: canali di comunicazione e predisposizione del protocollo di

test. In genere questo aumento di complessità dei dispositivi elettronici implica un aumento dei costi ed una riduzione delle prestazioni. La Collaborazione ANTARES ha però esigenze diverse rispetto ad una situazione di produzione industriale considerato che il numero totale dei moduli (~500) è esiguo rispetto ai volumi tipici delle catene di produzione di dispositivi commerciali e che la progettazione, l'integrazione e il test saranno effettuati da personale altamente qualificato e pienamente consapevole delle funzionalità in gioco. Pertanto ci si è orientati verso l'adozione di uno standard di test proprio come sarà illustrato nel paragrafo successivo.

Tuttavia, poiché lo standard BST (Boundary Scan Test) o anche noto come JTAG, è uno gli standard di test commerciali a maggiore diffusione, mi è parso opportuno richiamare, in un paragrafo successivo, alcuni tra i suoi principi ispiratori, nella eventualità che esso possa trovare opportuno impiego, nella realizzazione di un rivelatore di seconda generazione a scala maggiore.

# 4.2 Filosofia di Test in ANTARES

### 4.2.1 MTBF

Come già accennato nei capitoli precedenti uno tra i principali requisiti dei vari sistemi che compongono il detector è l'affidabilità. Essa può essere efficacemente specificata a partire dalla stima del MTBF. Si richiede un MTBF non inferiore a un milione di ore che corrisponde ad un numero di fallimenti

dell'ordine di  $1\sim2$  % in 10 anni. In realtà l'affidabilità, identificata nel seguito con il simbolo R ha la seguente definizione: "la probabilità che il componente fornisca ininterrottamente le prestazioni richieste fino a quell'istante, in condizioni di funzionamento specificate".

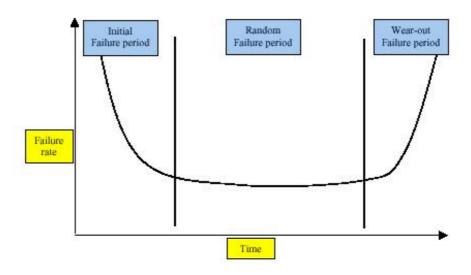

L'andamento nel tempo del tasso di guasto (cioè la percentuale di guasti valutati in una popolazione di componenti o sistemi) è efficacemente rappresentato dalla cosiddetta "curva a vasca da bagno" (figura 4-1), la cui forma caratteristica rimane pressoché invariata pur cambiando il tipo di dispositivo esaminato.

Figura 4-1. Curva detta a vasca da bagno che indica il numero di guasti in funzione del tempo. La curva si divide in tre parti: mortalità infantile, guasti casuali, guasti da logorio.

Il tratto iniziale della curva viene chiamato "mortalità infantile", cioè rappresenta il tasso di guasto di un prodotto nelle prime ore di funzionamento. Il tasso di guasto è generalmente più elevato in questo periodo a causa della scoperta di eventuali difetti di fabbricazione. All'altra estremità del grafico si può

individuare la zona di "mortalità dovuta a usura", durante la quale alcuni componenti elettronici iniziano a guastarsi per invecchiamento e deriva delle caratteristiche. Il tratto di curva compreso fra le due zone descritte è detto "vita utile". Nel tratto di curva indicato come "vita utile" si utilizza la seguente relazione:

$$R(t) = e^{-G \cdot t}$$

che esprime l'affidabilità in funzione del tasso di guasti G e del tempo. Si definisce MTTF (Mean Time To Failure) il tempo medio fino al guasto e si ottiene dalla relazione precedente per  $R(t) = e^{-t}$  cioè per MTTF = 1/G. Il MTTF e l'MTBF sono legati perché il primo rappresenta il tempo medio fino al guasto mentre il secondo rappresenta il tempo medio tra due guasti. Dunque il secondo è dato dal primo più il tempo necessario alla sostituzione del componente guasto e al ripristino delle funzionalità del prodotto finale. Attualmente però con una tecnologia capace di offrire tassi di guasto estremamente bassi, la differenza fra MTTF e MTBF risulta trascurabile, quindi i due valori sono praticamente coincidenti. Per questo motivo, anche se da un punto di vista teorico è più corretto parlare di MTTF, spesso nella pratica si parla di MTBF.

### 4.2.2 Standard di Test in ANTARES

Per ottenere valori elevati dell'MTBF occorre:

scegliere componenti che presentano MTBF più elevato possibile compatibilmente con la disponibilità e accessibilità di costo;

- progettare opportunamente sistemi elettronici e meccanici;

- definire un accurato programma di test comune in modo da eliminare i difetti di fabbricazione e di 'mortalità infantile' [33].

La fase di test appare, dunque, fondamentale per il buon funzionamento dell'intero apparato, soprattutto in considerazione della inaccessibilità del sito scelto.

La Collaborazione ha scelto di far realizzare parallelamente lo sviluppo dei sistemi elettronici e lo sviluppo dei banchi di test perché in questo modo si possono uniformare le procedure di test per migliorare la affidabilità di funzionamento dei sistemi elettronici e si possono utilizzare procedure di test a vari livelli per verificare la funzionalità di ogni sistema. Infatti essendo l'apparato costituito da molti sistemi e dispositivi, un modo che non crea ambiguità è il controllo dei singoli costituenti, dunque una scomposizione.

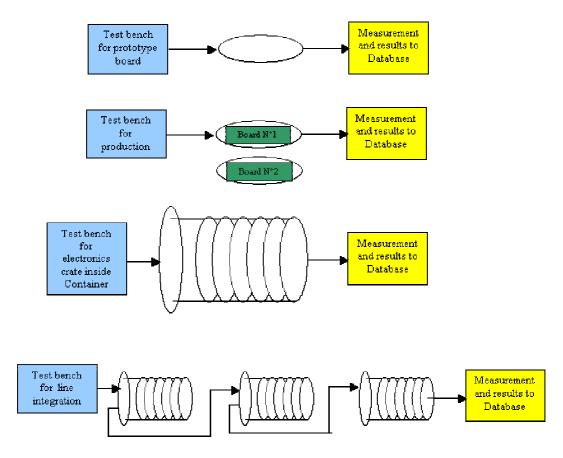

Il programma di test è stato scomposto in 3 fasi differenti:

- test delle schede prototipo: ogni progettista realizza una procedura di test e descrive le misure e i controlli effettuati attraverso l'hardware e il software di cui dispone.

- test di accettazione del fornitore: ogni scheda realizzata dal fornitore o da un

centro di ricerca per la catena di produzione è sottoposta ad un programma di test

per l'accettazione. Tali prove devono verificare ogni funzione della scheda e

comprendere prove di stress accelerato (prove per mettere in evidenza eventuali

difetti di produzione di alta e bassa temperatura, di vibrazione accelerazione).

- test di integrazione degli oggetti principali: dapprima le schede vengono

integrate all'interno dei moduli (LCM\_CRATE, SCM\_CRATE ecc.) e poi la funzionalità del modulo è controllata da un test bench, sviluppato per misurare e verificare la funzionalità dell'oggetto completo.

Ulteriori prove di test sono effettuate integrando insieme un intero settore o una stringa in cui occorre provare la funzionalità dei moduli e dei collegamenti. In figura 4-2 sono rappresentate schematicamente i tipi di prove da effettuare.

Figura 4-2. Prove di test da effettuare: test delle schede prototipo, test delle schede per la produzione, test dei moduli assemblati e test del settore o della stringa.

Le misure e le verifiche effettuate su tutti i dispositivi esaminati in tutte queste prove vengono memorizzate in un database. Questi vengono integrati insieme e costituiscono una base informativa utile per le successive prove di test.

# 4.3 Elenco delle funzioni da sottoporre a test

Poiché sono previsti diversi tipi di test, le cosiddette prove di integrazione (le ultime due elencate nel precedente paragrafo) vengono realizzate esaminando la funzionalità degli oggetti sotto test. Infatti, le prove in cui vengono effettuale le misurazioni e i controlli di tutte le variabili in gioco, sono rivelate su oggetti singoli dai centri di ricerca o dai produttori che li hanno realizzati e che dispongono di strumentazione adatta per tali test.

Dunque, anche per il test del modulo SCM le verifiche da effettuare sono di funzionalità. Pertanto è necessario utilizzare dispositivi che permettano di interfacciarsi con il modulo come se fosse presente nella stringa. Inoltre non occorre prevedere la verifica di tutti gli oggetti passivi poiché già provati e garantiti dai fornitori, nelle prime due fasi di test descritte. In definitiva il Test Bench non deve valutare la bontà dei dispositivi contenuti nel modulo SCM, in quanto questa è stata già valutata in altre sedi, ma piuttosto il fatto che integrati funzionino o meno e che non vi siano danni dovuti al trasporto. Nel caso in cui si riscontrassero malfunzionamenti, il compito del gruppo di Test Bench di Bari è quello di restituire la scheda difettosa al centro che l'ha prodotta e sostituirla con una funzionante.

Prima di descrivere gli oggetti da testare si ritiene utile riassumere le funzioni spettanti all'SCM:

- 1) distribuzione della alimentazione a ciascun settore della stringa;

- 2) trasmissione del segnale di trigger e della richiesta di lettura RoR da/verso

- ciascun settore della stringa;

- 3) trasmissione in DWDM dei dati raccolti dai diversi settori della stringa (i dati vengono multiplexati nell'SCM in modo da viaggiare su un'unica fibra verso la JB);

- trasmissione in DWDM dei comandi di SC verso i diversi settori della stringa

(i comandi vengono demultiplexati all'interno dell'SCM in modo da raggiungere il settore desiderato);

- 5) trasmissione del segnale di clock e di eventuali comandi di controllo ai diversi settori della stringa e esecuzione corretta dei comandi inviati verso l'SCM attraverso questa connessione;

- 6) trasmissione dei dati localmente prodotti;

- 7) risposta ai comandi di SC indirizzati all'SCM;

- 8) controllo dei componenti locali collegati all'SCM: l'SPM, il Laser Bacon, l'Acoustic Transponder, il Pressure Sensore, il Sound Velocimeter;

- elaborazione corretta dei segnali analogici provenienti dal Laser Beacon e dal Acoustic Transponder.

Il primo punto è realizzato dal blocco OPT\_CONV che contiene tutte le connessioni ottiche ed elettriche. Le connessioni elettriche riguardano le alimentazioni provenienti dall'SPM. Il blocco provvede allo smistamento di queste alimentazioni verso i settori e verso l'SCM. Poiché questa parte del modulo è completamente passiva non è necessario alcun test.

Il secondo punto è realizzato dalla scheda SCM\_SPLIT, connessa sul connettore numero 10, nel quale è presente uno splitter completamente passivo

che divide la potenza ottica in 6 parti, una per ciascun settore. Anche per questa funzione non è necessario alcun test.

Il terzo e quarto punto prevedono lo smistamento e riunificazione delle lunghezze d'onda che trasportano i dati, ad opera dei dispositivi MUX\_DWDM e DEMUX\_DWDM posti sulla scheda collegata al connettore numero 4. Poiché anche questa scheda contiene solo dispositivi passivi, le funzioni ai punti 3 e 4 non saranno testate.

In definitiva il Test bench deve verificare la completa funzionalità degli SCM per:

- la trasmissione del segnale di clock e di eventuali comandi di controllo ai diversi settori della stringa e esecuzione corretta dei comandi inviati verso l'SCM attraverso questa connessione;

- la risposta ai comandi di SC indirizzati all'SCM;

- il controllo dei componenti locali collegati all'SCM: l'SPM, il Laser Beacon,

l'Acoustic Transponder, il Pressure sensor, il Sound Velocimeter;

- l'elaborazione corretta dei segnali analogici provenienti dal Laser Beacon e dall'Acoustic Transponder.

# 4.4. Progetto del Test Bench

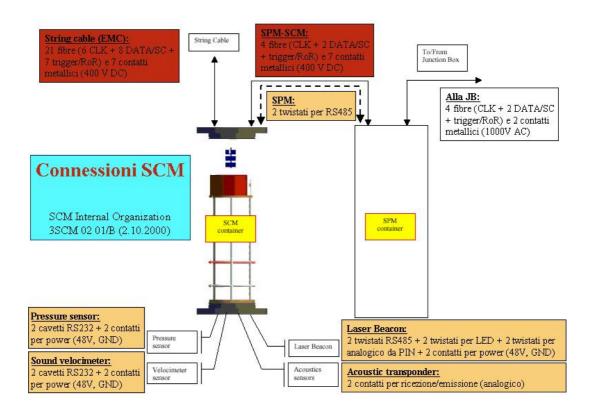

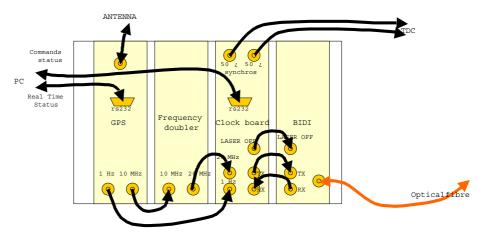

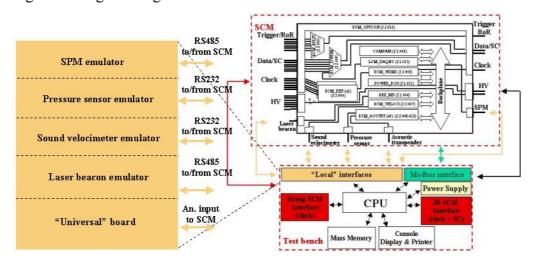

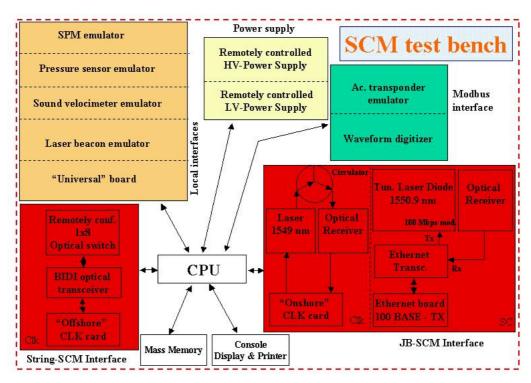

Nei precedenti paragrafi si è affermato che il compito del banco di prova è quello di verificare il modulo SCM simulando le condizioni di reale funzionamento. In realtà il modulo sarà alloggiato in laboratorio durante i test e sarà privo del suo involucro in modo da permettere l'accesso ai componenti interni. Per realizzare questa possibilità occorrerà costruire, pertanto, un certo numero di simulatori che consentano la reale operatività e nello stesso tempo raccolgano informazioni che permettano di assicurare il funzionamento di tutti i sistemi che l'SCM include. Uno schema è mostrato in figura 4-3.

Dunque occorrerà simulare:

- la comunicazione verso l'SCM attraverso la fibra dei dati che proviene dalla JB;

- la comunicazione sulla fibra di clock proveniente dalla JB;

- la comunicazione sulla fibra di clock proveniente dalla stringa;

- le comunicazioni da/verso SPM;

- le comunicazioni da/verso il Sound Velocimeter;

- le comunicazioni da/verso il Pressure Sensor;

- le comunicazioni da/verso il Laser Beacon;

- i segnali analogici provenienti dall'Acoustic Transponder e il Laser Beacon.

Figura 4-3. Schema e descrizione dei collegamenti dell'SCM.

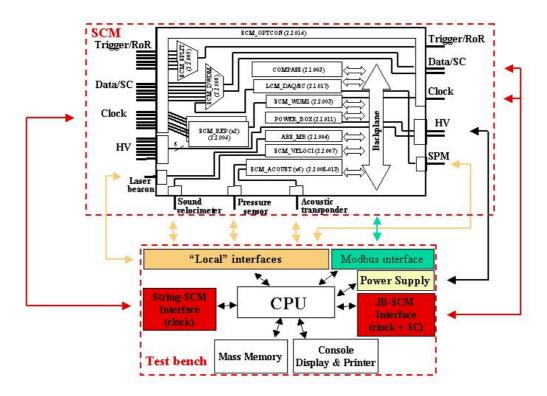

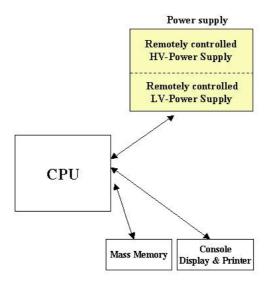

Un'altra esigenza che il Test Bench deve soddisfare è quella di essere completamente automatico. Ovvero, una volta effettuate le dovute connessioni tra il Test Bench e l'SCM, la fase di prova deve avvenire in completa autonomia, cioè senza nessun intervento manuale sulle connessioni. Questo per evitare interferenze che possono modificare il risultato della prova. Occorre, pertanto, disporre in elenco le verifiche da effettuare in modo automatico, cioè eseguendo le istruzioni di un programma. Quindi al centro del Test Bench deve essere previsto un processore che permetta di eseguire delle istruzioni prestabilite. Il processore deve anche memorizzare i dati o stamparli e rendere visibili i risultati parziali, pertanto occorre una memoria di massa, una console, un monitor e una stampante. Una configurazione che riunisce questi dispositivi è un personal computer.

Il Test Bench deve inoltre provvedere all'alimentazione dei dispositivi contenuti e del modulo SCM, per cui occorre inserire due alimentatori entrambi pilotabili attraverso il PC. Il primo alimentatore deve fornire 400 V DC e almeno 0.625 A, dal momento che il consumo previsto massimo dell'SCM è di circa 250W. Il secondo alimentatore deve fornire le basse tensioni per alimentare gli altri dispositivi.

Figura 4-4. Test Bench configurato a blocchi.

Per ridurre la complessità dell'intero banco di prova, ho immaginato di suddividerlo in blocchi, che saranno sviluppati nel seguito del paragrafo. La disposizione e la connessione di questi blocchi, può essere osservata in figura 4-4.

In figura 4-5 si possono osservare i blocchi che descrivono questa prima parte del Test Bench.

Figura 4-5. Schematizzazione dei primi blocchi del Test Bench.

I blocchi indicati sinteticamente nella figura 4-4, data la complessità e la numerosità dei sistemi che saranno oggetto della fase di test, saranno costituiti da numerosi dispositivi. Per motivi di opportunità la scelta sulla provenienza di questi dispositivi e ricaduta sulla strumentazione commerciale.

Un altro motivo che spinge ad adottare i dispositivi commerciali riguarda le connessioni fra i vari moduli. Infatti è noto che i dispositivi commerciali hanno la caratteristica di supportare standard di connessioni molto diffusi. Uno tra i più diffusi di questi sistemi è sicuramente lo standard GPIB (General Purpose Interface Bus) a causa della sua grande flessibilità. Dunque questo standard è stato scelto per supportare la maggior parte delle connessioni del banco di prova.

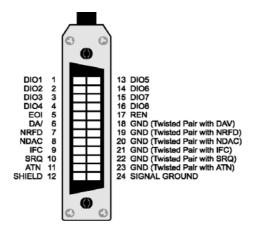

Lo standard GPIB, anche conosciuto con IEEE<sup>1</sup> 488 (con riferimento alle specifiche standard cui si riferisce), può supportare differenti tipologie di connessione tra gli schemi limite della configurazione lineare ed a stella (figura 4-6).

.

<sup>&</sup>lt;sup>1</sup> Institute of Electrical and Electronic Engineers

Figura 4-6. Schemi limite di connessione GPIB.

Un dispositivo GPIB può assumere le funzioni di 'parlatore', 'ascoltatore' o 'controllore'. Il parlatore manda dati ad uno o più ascoltatori, l'ascoltare accetta dati da un parlatore e il controllore gestisce il flusso dei dati sul bus. Solitamente il compito del controllore è assolto dal PC attraverso una scheda elettronica apposita. Il trasferimento dei dati avviene con un bus parallelo di 8 bits indicati DIO1..DIO8 che possono essere osservati in figura 4-7.

Figura 4-7. Descrizione dei segnali costituenti un connettore GPIB.

Di seguito saranno illustrati i simulatori che permettono di realizzare le funzioni citate all'inizio del paragrafo.

### 4.4.1. Data/SC provenienti dalla JB

Per simulare i dati o i comandi di SC che provengono dalla shore station, occorre necessariamente una sorgente che permetta di inviare segnali luminosi nella fibra dei dati e di un ricevitore che permetta di convertire i segnali luminosi provenienti dall'SCM in segnali elettrici da interpretare quale comunicazione proveniente dall'SCM.

La sorgente luminosa scelta è un laser a lunghezza d'onda fissa in particolare 1550.9 nm, la potenza ottica non è molto importante poiché la lunghezza del cavo è ridotta. Questa sorgente però deve essere modulata in modo da trasferire le informazioni in funzione dei segnali inviati. Esistono sorgenti laser già complete di modulatore e sorgenti in cui occorre inserire modulatori esterni. Esistono anche diversi tipi di modulatori: ad elettro-assorbimento, niobato di litio, di Mach Zendel ecc.

Una soluzione innovativa nella trasmissione ottica dei segnali, è rappresentata dai laser EML (Electroabsorptive Modulated Laser). Questi dispositivi sono realizzati mediante l'integrazione nello stesso chip di un laser a semiconduttore e di un modulatore ad "elettroassorbimento", ovvero a riflettività variabile con la tensione applicata. Un laser EML è composto da strati di fosfato di indio e arseniuro di gallio (GaAsInP) e fosfato di indio (InP), con le facce interne ondulate in modo da formare un reticolo alla Bragg fra le zone p ed n della giunzione, cioè un laser DBR (Distributed Bragg Reflector), che integra, però, anche un modulatore in niobato di litio (LiNbO<sub>3</sub>) ad assorbimento elettrocomandato, nel quale la polarizzazione è variabile con il campo elettrico:

applicando una tensione nella sezione terminale di uscita, si può cambiare la polarizzazione da TE a TM, facendone crollare drasticamente la riflettività, e permettendo dunque l'emissione della luce all'esterno; viceversa, ripristinando le condizioni di polarizzazione contrarie, l'emissione luminosa si spegne. Per il ricevitore è possibile usare un PIN o un APD (Avalanche Photo Diode) [34].

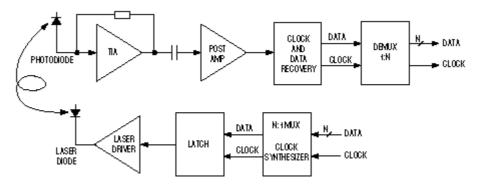

In figura 4-8 è mostrato lo schema a blocchi di un tipico transceiver per sistemi di comunicazioni in fibre ottiche. I blocchi superiori costituiscono il ricevitore, quelli inferiori, il trasmettitore. Il blocco dopo il fotodiodo nello schema è un amplificatore a transimpedenza (TransImpedance Amplifier – TIA) che converte un segnale di corrente quale quello proveniente dal fotodiodo in un segnale di tensione che viene successivamente amplificato dal blocco successivo. Dopo essere amplificato il segnale viene inviato nel blocco CDR (Clock and Data Recovery) che permette il recupero dei dati e del segnale di clock. I dati e il segnale di clock vengono quindi inviati in un deserializzatore. Nel trasmettitore costituito dai blocchi rappresentati nella parte inferiore della figura i segnali si propagano da destra verso sinistra. I dati vengono dapprima serializzati e poi mantenuti stabili da un elemento di memoria (latch). Vengono quindi trasmessi al diodo laser attraverso un laser driver [35].

Figura 4-8. Tipico schema a blocchi di un transceiver per sistemi in fibra ottica.

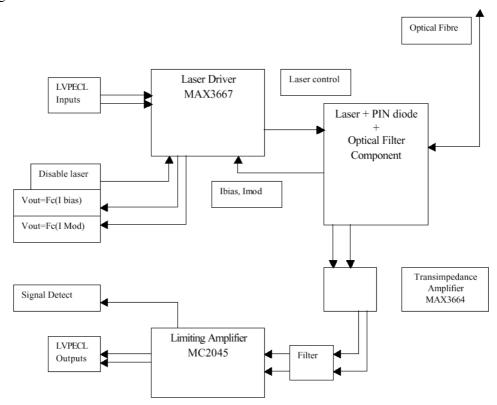

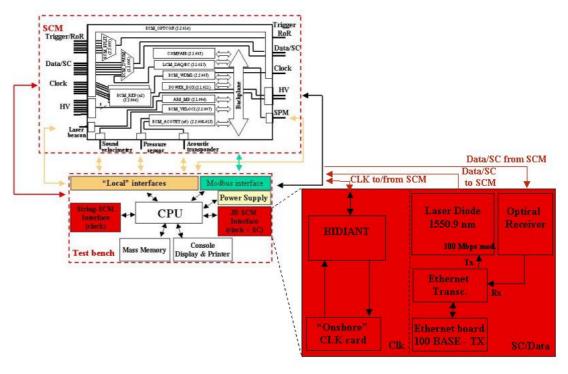

Una possibilità particolarmente promettente e di costo contenuto che ho valutato consiste nell'utilizzare il transceiver BIDIANT opportunamente modificato per formare la prima parte della catena di blocchi precedentemente illustrata. Infatti osservando lo schema a blocchi del BIDIANT (mostrato in figura 4-9) [27] è possibile notare il Laser Driver MAX3667 e l'amplificatore a transimpedenza MAX3664 della compagnia MAXIM e l'amplificatore MC2045 della Microcosm Comunication utilizzato per fornire il necessario guadagno per il segnale di uscita ECL.

Figura 4-9. Schema a blocchi del BIDIANT.

La seconda parte dello schema a blocchi deve essere realizzata da dispositivi integrati opportuni che permettano la conversione dei segnali ECL provenienti dal BIDIANT in segnali da connettere ad una scheda Ethernet 100 BASE - TX attraverso ad esempio il connettore MII (Medium Indipendent Interface). La scheda

Ethernet a sua volta sarà connessa al personal computer che fornirà e memorizzerà i dati scambiati. Un dispositivo adatto a tale scopo è ad esempio LXT 970A della compagnia Level1 [36].

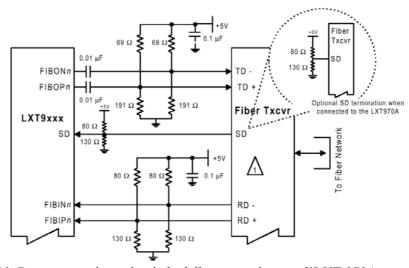

In figura 4-10 è rappresentato uno schema circuitale della connessione tra l'LXT 970A con un generico dispositivo che trasmette in standard PECL attraverso i pin FIBON, FIBOP, FIBIN e FIBIP.

Figura 4-10. Rappresentazione circuitale della connessione tra l'LXT 970A con un generico dispositivo che trasmette segnali PECL.

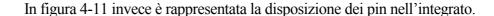

Figura 4-11. Disposizione dei pin nell'integrato l'LXT 970A.

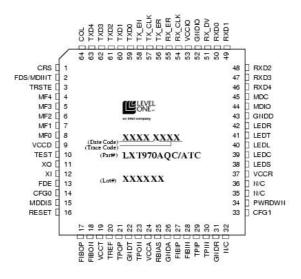

La connessione invece tra l'integrato LXT 970A e la scheda Ethernet avviene collegando i pin: RX\_DV, RX\_CLK, RX\_ER, RX\_D<4:0>, CRS, COL e TX\_CLK ai rispettivi pin del connettore MII rappresentato nella figura 4-12.

Figura 4-12. Disposizione dei pin nel connettore MII.

# 4.4.2. Comunicazione sulla fibra di clock proveniente dalla JB

Poiché il clock viaggia su fibra ottica anche in questo caso occorre utilizzare un laser e un ricevitore PIN. Inoltre la Collaborazione fornirà le schede elettroniche di trasmissione del clock della shore station, il cui schema è rappresentato in figura 4-13.

Figura 4-13. Schema delle schede elettroniche che si occupano dei segnali di clock nella shore station.

Nel test del sistema di clock, non occorre un riferimento preciso, pertanto non saranno utilizzati i dispositivi GPS e raddoppiatore di frequenza mostrati in figura 4-13. I dati inviati sul segnale di clock saranno forniti e ricevuti dal personal computer attraverso la porta seriale RS232 disegnata in figura.

Si ricorda che i ricevitori di impulsi luminosi PIN sono sensibili in un ampio intervallo di lunghezze d'onda del segnale. Ciò vale anche per quelli presenti sulla scheda SCM\_WDM1 contenuta nell'SCM. Pertanto è possibile utilizzare un transceiver BIDIANT al posto del laser e del PIN ipotizzati, con un notevole risparmio dei costi e dei tempi necessari per la progettazione di un transceiver adatto.

In figura 4-14 è mostrato lo schema a blocchi della parte di Test Bench indicata con 'JB-SC Interface', che realizza la trasmissione dei dati e dei segnali di clock provenienti dalla shore station.

Figura 4-14. Schema a blocchi della 'JB-SCM Interface'.

# 4.4.3. Comunicazione sulla fibra di clock proveniente dalla stringa

Le fibre di clock che fuoriescono dal modulo SCM verso i settori della stringa sono 6. Pertanto occorrerebbero 6 sistemi di comunicazione indipendenti. Tuttavia, poiché non è necessario che i canali lavorino contemporaneamente, è possibile realizzarne uno per poi utilizzarlo in sei momenti differenti. Poiché il Test Bench deve essere automatico occorre, dunque, un dispositivo che commuti i segnali ottici provenienti dalle diverse fibre verso l'unico sistema di comunicazione realizzato. Questo dispositivo si chiama Optical Switch e permette di commutare i segnali che viaggiano su una fibra verso una tra altre otto fibre. Per il componente ipotizzato è richiesta la possibilità di essere controllabile in remoto, cioè la commutazione può essere comandata da un personal computer.

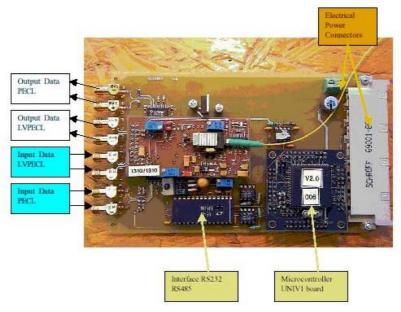

Il sistema di comunicazione da implementare, dunque, deve comunicare attraverso segnali ottici con uno tra i 6 dispositivi BIDIANT presenti sulle schede SCM\_REP, pertanto anche in questo caso si può utilizzare come transceriver un dispositivo BIDIANT 2 che utilizza lunghezze d'onda opposte a quelle utilizzate da quello presente nell'SCM, pertanto utilizzerà 1310 nm per trasmettere e 1550 nm per ricevere.

Per poter dialogare con il dispositivo BIDIANT, esiste un'interfaccia che adopera attraverso una porta seriale RS232. Per cui, il dispositivo completo (BIDIANT+interfaccia) è chiamato BIDIDEV. Tale dispositivo può essere osservato in figura 4-15.

Figura 4-15. Fotografia del dispositivo BIDIDEV, con installata la scheda BIDIANT.

Dunque, attraverso un programma posto nel personal computer è possibile simulare i dati di risposta ai comandi inviati dal sistema del clock della shore station. Per esaminare la correttezza del segnale di clock trasmesso dall'SCM verso i settori della stringa basterà esaminare la corrispondenza tra i segnali elettrici trasmessi e quelli ricevuti.

In figura 4-16 è mostrato lo schema a blocchi della parte di Test Bench indicata con 'String-SCM Interface', che comprende la trasmissione dei segnali di clock provenienti dalla stringa.

Figura 4-16. Schema a blocchi dell' 'String-SCM Interface'.

### 4.4.4. Comunicazioni da/verso Pressure Sensor e Sound Velocimeter

Le comunicazioni con i dispositivi Pressure Sensor e Sound Velocimeter avvengono tramite standard seriale RS232. Queste comunicazioni saranno descritte in maggior dettaglio nel capitolo successivo.

# 4.4.5. Comunicazioni da/verso SPM e Laser Beacon

Le comunicazioni con i dispositivi SPM e Laser Beacon avvengono mediante lo standard RS485 con protocollo MODBUS. Anche queste comunicazioni saranno descritte nel capitolo successivo.

# 4.4.6. Segnali analogici provenienti dall'Acoustic Transponder e Laser Beacon

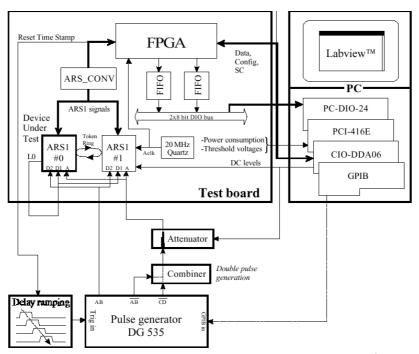

Per generare i segnali analogici necessari alla simulazione del comportamento dell'Acoustic Transponder e del Laser Beacon è possibile utilizzare un generatore di impulsi. Una configurazione interessante è mostrata in figura 4-17, che rappresenta lo schema del Test Bench del circuito ARS1 [37]. In questo schema è stato utilizzato il generatore di impulsi DG535 della compagnia SRS [38], un attenuatore e un combinatore. Quest'ultimo in particolare è necessario nel dispositivo illustrato per ottenere forme d'onda con impulsi doppi, utilizzati per simulare segnali di tipo WF, ma non sarà richiesto nel Test Bench dell'SCM poiché questo raccoglie solo i segnali provenienti dal Laser Beacon. Pertanto è possibile proporre una configurazione composta dallo stesso DG535 della SRS e un'attenuatore.

Figura 4-17. Schema a blocchi del Test Bench del circuito ARS1. È ben visibile il generatore di impulsi in basso a destra.

In figura 4-18 è mostrato lo schema a blocchi della parte di Test Bench indicata come 'Local Interface', che simula le comunicazioni da e verso il modulo SPM, il Pressure Sensor, il Sound Velocimeter, il Laser Beacon, ed emula i segnali analogici in ingresso all'SCM.

Figura 4-18. Schema a blocchi dell' 'Local Interface'.

### 4.4.7. Schema del Test Bench

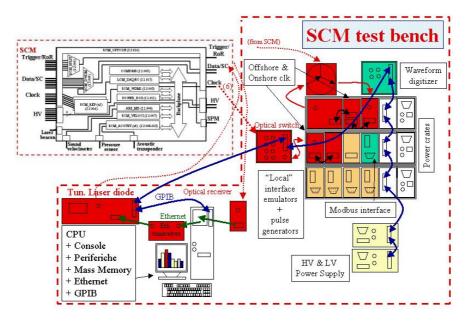

A completamento del progetto del banco di prova, occorre aggiungere due ulteriori dispositivi necessari per garantire un test accurato del modulo SCM.

Il primo dispositivo è un waveform digitizer. Questo dispositivo è una sorta di oscilloscopio numerico che permette di interfacciarsi direttamente con un personal computer e di acquisire informazioni su forme d'onda per successive elaborazioni. Questo dispositivo è utile per controllare il tipo di segnale analogico inviato verso la scheda ARS\_MB e verso le schede di posizionamento acustico e per garantire che la tipologia di questi segnali è conforme con quella richiesta dalla Collaborazione.

Il secondo dispositivo deve permettere di controllare il flusso dei dati che

transitano sul bus seriale dell'SCM con protocollo MODBUS. Dunque sarà predisposto un'ulteriore connettore oltre a quelli previsti sul backplane dell'SCM per permettere questa comunicazione. L'importanza di questa ulteriore funzionalità, aggiunta al banco di prova, deriva dalla considerazione che non tutte le schede interne dell'SCM sono connesse direttamente verso l'esterno, dunque un controllo dei dati che riguardano queste schede diventa molto utile ai fini della verifica di funzionamento.

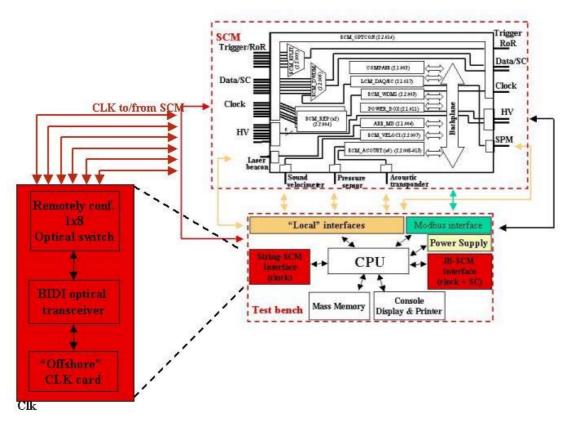

Mi sembra utile riassumere quanto descritto in questo paragrafo attraverso un diagramma a blocchi che comprende tutti i sottosistemi elencati, mostrato in figura 4-19.

Figura 4-19. Schema a blocchi del Test Bench.

In figura 4-20 si può osservare uno schema più dettagliato dei precedenti in cui è mostrata la disposizione e i collegamenti tra i vari blocchi che

costituiscono il Test Bench ai fini di una maggiore compattezza ed organicità.

Figura 4-20. Schema a blocchi del Test Bench.

# 4.5. Estensione del progetto del Test Bench ad un settore o ad una stringa

Data la cruciale disposizione del modulo SCM all'interno della stringa è ragionevole ipotizzare una possibile estensione del banco di prova per l'SCM a banco di prova per un settore o una stringa completa. Questa possibilità deriva dalla considerazione che tutti i dati e i segnali che viaggiano su una stringa sono convogliati attraverso SCM, e che in particolare questo modulo ha la funzione unica, di smistare e riunire i segnali sulle fibre dei dati. Inoltre, le lunghezze d'onda su cui viaggiano i dati sono diverse per i vari settori, ma l'assegnazione è la stessa per tutte le stringhe.

Come già detto il test di un settore o di una stringa (come quello dell'SCM) è previsto per funzionalità. Quindi i vari moduli citati devono essere interpellati e deve esserne verificato il corretto funzionamento.

Nonostante il fatto che il test bench progettato sia una buona base di partenza per lo sviluppo del test bench di un settore o di un'intera stringa, occorre, tuttavia, apportare delle variazioni e inserire degli apparati supplementari. Si ritiene, pertanto, conveniente elencare dapprima le funzionalità da testare, che saranno sviluppate nel seguito del paragrafo.

- Data/SC;

- Clock;

- Trigger;

- Controllo dell'alimentazione.

Nel seguito discuterò la possibilità di estensione a banco di test di una intera stringa: evidentemente il test di un settore realizza un caso particolare di questa possibilità.

### 4.5.1. Data/SC

Il test di funzionamento del sistema di Data/SC può essere realizzato valutando uno tra i 7 canali per volta. Infatti vi sono 6 canali corrispondenti ai settori ed uno al modulo SCM. Poiché su questi canali occorre far transitare dati in forma di impulsi luminosi a diverse lunghezze d'onda, è necessaria una sorgente luminosa la cui lunghezza d'onda possa variare in un range stabilito (1549.3 nm – 1560.6 nm).

Una difficoltà ulteriore, non prevista nel Test Bench dell'SCM, è la possibilità di gestire entrambi i flussi di dati (quelli provenienti dall'SCM e quelli provenienti dall'MLCM) in quanto, mentre sul canale assegnato all'SCM transitano dati con flusso pari a 100 Mbit/s, sui canali relativi ai settori il flusso di dati deve essere pari a 1 Gbit/s. La sorgente 'tunable' deve avere, dunque, caratteristiche di modulabilità più avanzate di quelle richieste nel Test Bench dell'SCM.

Anche la scheda Ethernet deve essere, pertanto, adeguata al flusso dei dati previsto. Tuttavia, mentre è certamente realizzabile la modulazione su entrambi i flussi di dati, non è detto che una scheda Giga Ethernet permetta il flusso di 100 Mbit/s. Infatti mentre la prima utilizza un interfaccia di collegamento chiamata GMII (Giga Medium Indipendent Interface), la seconda utilizza un'altra interfaccia, chiamata MII. In ogni modo è possibile utilizzare un'unica scheda Ethernet 1000 BASE – T purché supporti un particolare protocollo, chiamato 'protocollo di autonegoziazione' che implementa entrambi i tipi di circuiti. Questo protocollo, infatti, permette di stabilire il flusso dei dati che transitano sul mezzo in base al tipo di schede Ethernet presenti sulla rete adeguandosi al flusso minore (10/100/1000 Mbit/s) [29].

### 4.5.2. Clock

Poiché i moduli MLCM sono presenti nel test della stringa, non v'è necessità di introdurre dispositivi per simulare i segnali di clock verso la stringa (a differenza di quanto avveniva nel test dell'SCM). Dunque, i dispositivi previsti

nel Test Bench dell'SCM sono in grado di verificare anche la funzionalità del sistema di clock di tutta la stringa.

# **4.5.3.** Trigger

Nel Test Bench dell'SCM non era preventivata nessuna verifica del funzionamento del sistema di trigger, pertanto questa funzionalità è nuova. Tuttavia il simulatore che occorre per verificare il funzionamento del sistema di trigger nei moduli LCM è costituito dalla scheda elettronica presente nella JB, chiamata JB\_TRIG1. In aggiunta, però, occorre prevedere un opportuna interfaccia che permetta il collegamento della scheda citata con il personal computer gestore della fase di test.

### 4.5.4. Controllo dell'alimentazione

Oltre a prevedere un'alimentazione che permetta di fornire corrente verso tutta la stringa attraverso il modulo SPM, è necessario svolgere una accurata verifica delle variabili elettriche in gioco, in quanto l'assorbimento e il numero dei moduli connessi è rilevante. Occorre dunque prevedere un'alimentazione (1000 V AC) da fornire all'SPM e un dispositivo che permetta il controllo delle variabili elettriche ad alta tensione, inoltre questi alimentatori devono essere pilotabili attraverso il PC con la porta GPIB.

# 4.6. Proposta di studio BST

Lo standard BST è sicuramente tra i più diffusi sistemi di test per la verifica di funzionalità per IC e schede elettroniche contenenti IC. Esso è esistente da lungo tempo e presenta una notevole disponibilità di dispositivi e software dedicati. In questo paragrafo introduco concetti che sono alla base del suo funzionamento.

Innanzitutto conviene collocare lo standard BST nel suo contesto storico: nel 1985 un gruppo dei fornitori europei ha formato il Joint European Test Action Group (JETAG) per studiare il test delle schede elettroniche. Con l'aggiunta delle aziende nordamericane, JETAG si è trasformato nel Joint Test Action Group (JTAG) nel 1986. Lo standard di test JTAG ha costituito la base dello standard IEEE 1149.1 (Test Port e Boundary-Scan Architecture IEEE 1149.1b, 1994) [39].

Le nozioni che stanno alla base del funzionamento dello standard BST sono contenute in una serie di tecniche denominate Tecniche di Scan Design [40]. Le tecniche di Scan Design sono un insieme dei metodi strutturati per progettare la testabilità dei circuiti sequenziali.

La difficoltà maggiore nel verificare i circuiti sequenziali è costituita dalle condizioni interne del circuito. Le tecniche di Scan Design permettono di controllare le condizioni interne d'un circuito sequenziale, dunque il problema di verificare un circuito sequenziale è ridotta alla verifica di un circuito combinabile, poiché le condizioni interne del circuito sono già sotto controllo.

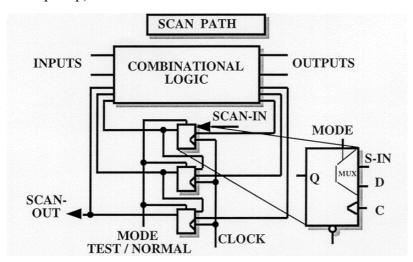

#### 4.6.1. Scan Path

L' obiettivo della tecnica scan path è la riconfigurazione di un circuito sequenziale in un circuito combinatorio per il test. Poiché un circuito sequenziale generico è composto da un circuito combinatorio e da alcuni elementi di memoria, la tecnica del scan path consiste nel collegare insieme tutti gli elementi di memoria per formare un lungo registro a scorrimento seriale. Così la condizione interna del circuito può essere osservata e gestita spostando verso l'esterno il contenuto degli elementi di memoria. Il registro a scorrimento, allora, è chiamato 'scan path'.

Gli elementi di memoria possono essere del tipo flip-flop D, J-K, o R-S (naturalmente i semplici latch non possono essere usati nello scan path). Tuttavia, la struttura degli elementi di memoria è un po' differente da quella classica. Generalmente la selezione dell'input è realizzata per mezzo di un multiplexer controllato da un segnale esterno. In figura 4-21 è rappresentato un multiplexer integrato in un flip-flop D, quindi il flip-flop D è chiamato MD-flip-flop (Multiplexed flip-flop).

Figura 4-21. Circuito sequenziale costituito da una memoria e da un circuito combinatorio.

Il circuito sequenziale che contiene uno scan path ha due modi di funzionamento: un modo normale e un modo test. Nel modo normale, gli elementi di memoria sono collegati al circuito combinatorio nel loop per formare un circuito sequenziale globale, considerato come una macchina a stati finiti.

Nel modo test, il loop è rotto e gli elementi di memoria sono collegati insieme come registro a scorrimento seriale (scan path), ricevente lo stesso segnale di clock. L'ingresso dello scan path è chiamato scan-in e l'uscita scan-out. Parecchi scan path possono essere effettuati in un stesso circuito complesso se è necessario, purché si abbiano vari ingressi scan-in e uscite scan-out. Un grande circuito sequenziale può essere diviso in circuiti secondari. Ciò serve per aumentare l'efficienza della generazione dei percorsi di test.

Prima dell'applicazione dei Test Pattern, il registro a scorrimento deve essere verificato cambiando tutti gli uno in zero o viceversa e confrontando che tutti gli elementi di memoria contengano il dato corretto.

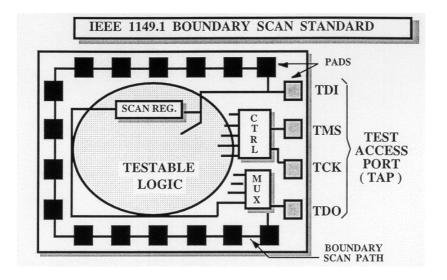

### 4.6.2. BST

Boundary Scan Test (BST) è una tecnica che coinvolge lo scan path e le tecniche di self-testing per risolvere il problema di testare le schede che trasportano circuiti integrati VLSI (Very Large Scale Integration) in particolare ASIC.

Per includere il BST su un ASIC, si aggiunge una cella di memoria ad ogni terminale d'ingresso/uscita dell'ASIC, come mostra la figura 4-22. Queste

celle unite insieme formano una catena e creano un registro a scorrimento chiamato registro boundary-scan che cinge ogni ASIC<sup>2</sup>.

Figura 4-22. Schema di principio di un IC che include BST

In ingresso al registro a scorrimento vi è l'immissione dei dati di test (TDI), mentre in uscita l'emissione dei dati di test (TDO). Questi registri a scorrimento si collegano in modo seriale uno all'altro per formare un lungo registro. Il registro a scorrimento boundary-scan è uno dei tanti registri per i dati di test (TDR) che possono essere inclusi in ogni ASIC, ma tutti i TDR in un ASIC sono collegati direttamente fra le porte di TDO e di TDI.

Per controllare tutti i funzionamenti in questione nella selezione dei registri, come il carico dei dati di test o lo spostamento verso l'esterno dei risultati, si usano i segnali Test Clock (TCK) e selezione test-mode (TMS).

Lo standard boundary-scan per questo motivo specifica un'interfaccia di

\_

<sup>&</sup>lt;sup>2</sup> Per la loro posizione prossima ai bordi, appunto Boundary dei chip, le celle vennero definite Boundary Scan Cell e la denominazione venne estesa alla procedura, appunto Boundary Scan Test (letteralmente: test tramite la scansione dei confini).

test a quattro vie con l'uso di quattro segnali: TDI, TDO, TCK e TMS. Questi segnali dedicati costituiscono la porta di accesso al test e sono collegati ad un controllore chiamato TAP, all'interno di ogni ASIC. Il controllore TAP è una macchina a stati finiti che è attivo sul fronte di salita del clock TCK con le transizioni gestite dal segnale di TMS. Il segnale in ingresso test-reset (TRST un segnale attivo sempre sul fronte di discesa) è un quinto segnale facoltativo dedicato all'interfaccia per effettuare un reset del controllore TAP.

Normalmente le celle del registro a scorrimento boundary-scan ad ogni terminale dell'ingresso/uscita dell'ASIC sono trasparenti. Dunque esse permettono il passaggio di segnali tra i terminali e i dispositivi logici interni. Quando un ASIC è posto in modo boundary-scan test, in primo luogo viene comunicato al controllore TAP quale TDR selezionare. Il controllore TAP, quindi, ordina ad ogni appropriato registro a scorrimento boundary-scan TDR se bloccare i dati di input, per spostare i dati alla cella vicina, o ai dati verso i terminali.

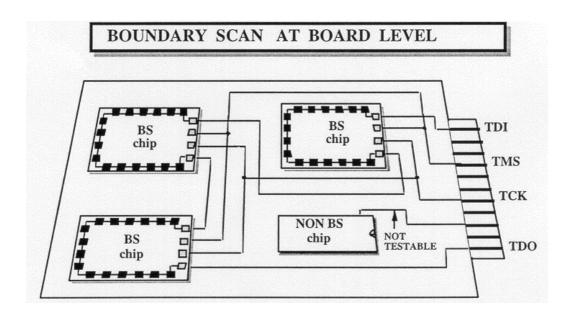

### 4.6.3. BST a livello di scheda

Più circuiti integrati sulla stessa scheda possono essere sono collegati insieme per formare un lungo singolo percorso attraverso la scheda. Naturalmente solo gli ASIC che contengono i circuiti BST possono essere testati, come mostra la figura 4-23.

Dunque per applicare il BST a livello di scheda occorre che la scheda sia fornita di terminali di ingresso e uscita seriali (TDI e TDO) e di collegamenti adatti per il segnale di clock (TCK) e di selezione test-mode (TMS). Ciò permette di:

Figura 4-23. Schema di principio di una scheda con implementazione del BST per alcuni IC.

- verificare le interconnessioni fra i vari circuiti integrati;

- trasportare i dati di test ai circuiti integrati a bordo per il self-testing;

- esaminare gli stessi circuiti integrati attraverso l'autoverifica interna.

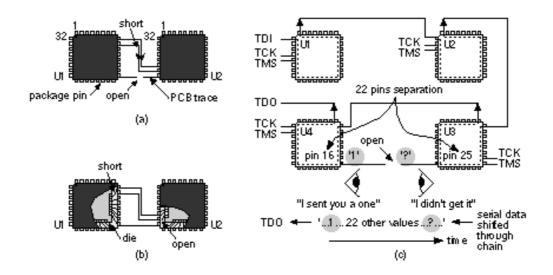

La figura 4-24 illustra alcuni esempi di guasti che possono accadere su una scheda dovuti a cortocircuiti o interruzioni nelle tracce di rame [39]. Guasti meno frequenti all'interno di un ASIC possono anche derivare da cortocircuiti o da interruzioni nei legami fra il monolite ed i contatti esterni. Questi guasti possono insorgere durante la produzione dell'ASIC, a causa di sollecitazioni durante il trattamento complessivo automatizzato non presenti nella produzione di prova.

La figura 4-24 (c) mostra come un gruppo di ASIC è collegato insieme mediante boundary scan per testare ogni connessione su una scheda. Durante il

boundary scan, i dati di prova sono caricati in ogni ASIC e poi inviati sulla scheda che segue. Ogni ASIC controlla i suoi dati di ingresso, cattura i dati ricevuti, quindi sposta i dati catturati in uscita. Tutti i difetti nella scheda o i collegamenti di ASIC verranno rivelati come discrepanza fra i dati previsti e quelli realmente misurati.

Figura 4-24. Esempi di guasti che possono accadere in una scheda: (a) interruzione di una traccia di rame o cortocircuito tra due linee di collegamento tra i IC diversi; (b) cortocircuito in un IC; (c) esempio di come il collegamento tra IC in fase di test permette di localizzare il guasto.

### Dunque i vantaggi del BST sono:

- il lavoro in fase di test è facilitato ed efficiente;

- non c'è esigenza di sviluppo di hardware complesso per il test della scheda;

- il tempo da impiegare nella progettazione e nell'esecuzione del test è ridotto e il numero di difetti rivelati è in genere superiore rispetto a test esterni.

Generalmente le grandi società produttrici di componenti e schede elettroniche, dovendo testare un elevato numero di dispositivi in catena di

montaggio, perciò in modo automatico, hanno spostato l'azione del test dall'esterno all'interno degli stessi dispositivi anche perché l'incremento di miniaturizzazione e la complessità dei componenti elettronici montati sulle schede hanno reso sempre più difficoltosi i tradizionali metodi di collaudo. Inoltre la densità dei componenti é aumentata a tal punto che l'accessibilità fisica é realizzabile con difficoltà sempre maggiore. Poi la maggior parte delle apparecchiature di test tradizionali, non può garantire una buona rivelazione dei difetti. Dunque, le soluzioni di test diventavano talmente complesse da realizzare e di costi tanto elevati, da inficiare i benefici.

Una buona analogia all'utilizzo al BST allo stato attuale potrebbe essere l'interfaccia RS232 per i personal computer. L'interfaccia standard di BST è infatti destinata alla verifica delle schede, ma è egualmente utile per comunicare con i circuiti ASIC, cioè fornisce i mezzi standard di comunicazione con circuiti IC. Per esempio questo standard è adottato in ANTARES come porta per programmare il circuito FPGA nel circuito RARS e per programmare la memoria EEPROM (Electrical Erasable Programmable Read Only Memory) attraverso un personal computer.